# Contents

| Features                         | 1 |

|----------------------------------|---|

| Applications                     | 1 |

| Pin Assignment                   | 1 |

| Block Diagram                    | 1 |

| Terminal Description             | 2 |

| Mode Table                       | 2 |

| Absolute Maximum Ratings         | 2 |

| Recommended Operating Conditions | 2 |

| DC Electrical Characteristics    | 3 |

| AC Electrical Characteristics    | 3 |

| Read Mode Operation              | 4 |

| Counter Hold Mode Operation      | 4 |

| Program Mode Operation           | 5 |

| Input Priority                   | 6 |

| Notes                            | 6 |

| Dimensions                       | 7 |

| Characteristics                  | 8 |

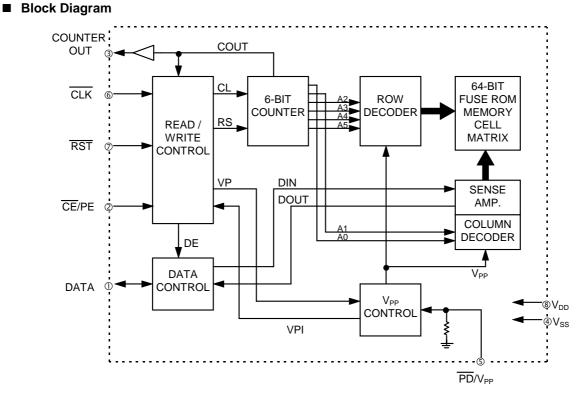

### 64-bit FUSE ROM

# S-2100R

The S-2100R is a CMOS 64-bit serial FUSE ROM. It has a low standby current (0.3  $\mu$ A max., V<sub>DD</sub>=1.5 V) and has a wide operating voltage range. Data can be read serially by clock pulses from address 1 to address 64. All the addresses are initialized at "H" so writing into "L" can be done only once.

#### Features

- Low standby current (0.3  $\mu$ A max., V<sub>DD</sub>=1.5 V)

- Wide operating voltage range

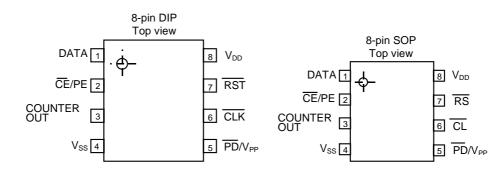

#### Pin Assignment

#### Applications

- Pager ID ROM

- Cordless telephone

- Security equipment

Figure 2

### Terminal Description

#### Table 1

| Pin No. | Symbol                          | Pin Name                       | Description                                                                                                                   |  |  |

|---------|---------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1       | DATA                            | Data input/output terminal     | Tri-state data input/output terminal                                                                                          |  |  |

| 2       | CE/PE                           | Mode select terminal           | Mode select terminal<br>(Refer to operation mode table)                                                                       |  |  |

| 3       | COUNTER<br>OUT                  | Counter output terminal        | 6-bit counter; 64th bit detection output terminal                                                                             |  |  |

| 4       | V <sub>SS</sub>                 | Negative power supply terminal | Normally, connected to GND.                                                                                                   |  |  |

| 5       | P <sub>D</sub> /V <sub>PP</sub> | Program voltage input terminal | Input terminal of writing voltage to FUSE memory at 21 V.<br>(Refer to operation mode table.) Pull-down resistor built<br>in. |  |  |

| 6       | CLK                             | Clock input terminal           | Clock input terminal of 6-bit counter. Operates at the falling edge.                                                          |  |  |

| 7       | RST                             | Reset input terminal           | Reset input terminal of 6-bit counter. Operates at "L".                                                                       |  |  |

| 8       | $V_{DD}$                        | Positive power supply terminal | Normally, connected to +1.1 to +5.5 V.                                                                                        |  |  |

### Mode Table

| Table 2           |                 |                         |                  |                  |                |  |  |

|-------------------|-----------------|-------------------------|------------------|------------------|----------------|--|--|

| l erminal<br>Read | CE/PE           | $\overline{P}_D/V_{PP}$ | CLK              | RST              | DATA           |  |  |

| Read              | $V_{SS}$        | V <sub>SS</sub>         | Input possible   | Input possible   | Data output    |  |  |

| Counter hold      | V <sub>DD</sub> | V <sub>SS</sub>         | Input impossible | Input impossible | High impedance |  |  |

| Program           | $V_{DD}$        | V <sub>PP</sub>         | Input impossible | Input impossible | Data input     |  |  |

# ■ Absolute Maximum Ratings

| Table 3                                       |                   |                                                    |      |  |  |

|-----------------------------------------------|-------------------|----------------------------------------------------|------|--|--|

| Parameter                                     | Symbol            | Ratings                                            | Unit |  |  |

| Power supply voltage                          | V <sub>DD</sub>   | -0.3 to +6.5                                       | V    |  |  |

| P <sub>D</sub> /V <sub>PP</sub> input voltage | V <sub>PP</sub>   | -0.3 to 26                                         | V    |  |  |

| Input voltage                                 | V <sub>IN</sub>   | $V_{\text{SS}}$ -0.3 to $V_{\text{DD}}\text{+}0.3$ | V    |  |  |

| Output voltage                                | V <sub>OUT</sub>  | $V_{\text{SS}}$ -0.3 to $V_{\text{DD}}\text{+}0.3$ | V    |  |  |

| Storage temperature<br>under bias             | $V_{\text{bias}}$ | -30 to +85                                         | °C   |  |  |

| Storage temperature                           | V <sub>stg</sub>  | -40 to +125                                        | °C   |  |  |

### Recommended Operating Conditions

### Table 4

| Parameter                | Symbol           | Conditions                           | Min.                 | Тур. | Max.            | Unit |

|--------------------------|------------------|--------------------------------------|----------------------|------|-----------------|------|

|                          | V <sub>DD</sub>  | Ta=25°C, Read, t <sub>CH</sub> =15µs | 1.1                  | 1.5  | 5.5             | V    |

| Power supply voltage     |                  | Ta=25°C, Write                       | 4.5                  | 5.0  | 5.5             | V    |

| High level input voltage | V <sub>IH</sub>  | Ta=25°C, Read                        | V <sub>DD</sub> -0.3 |      | V <sub>DD</sub> | V    |

|                          |                  | Ta=25°C, Write                       | V <sub>DD</sub> -0.3 |      | V <sub>DD</sub> | V    |

| Low level input voltage  | V <sub>IL</sub>  | Ta=25°C, Read                        | -0.3                 |      | 0.3             | V    |

|                          |                  | Ta=25°C, Write                       | -0.3                 |      | 0.5             | V    |

| Operating temperature    | V <sub>opr</sub> |                                      | -20                  | _    | 70              | °C   |

### **DC Electrical Characteristics**

### Table 5

| Parameter                             | Symbol           | Conditions                                                                                             | Min. | Тур. | Max. | Unit |

|---------------------------------------|------------------|--------------------------------------------------------------------------------------------------------|------|------|------|------|

| Operating current consumption         | I <sub>DDO</sub> | V <sub>DD</sub> =1.5 V, f <sub>CLK</sub> =50 kHz                                                       |      |      | 20   | μΑ   |

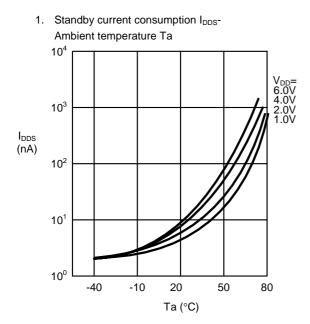

| Standby current consumption           | I <sub>DDS</sub> | V <sub>DD</sub> =1.5 V, <del>RS</del> T=V <sub>DD</sub><br>CLK=V <sub>DD</sub> , CE/PE=V <sub>SS</sub> | _    | _    | 0.3  | μΑ   |

| $\overline{P_D}/V_{PP}$ input voltage | V <sub>PP</sub>  |                                                                                                        | 20   | 21   | 22   | V    |

| $\overline{P_D}/V_{PP}$ input current | I <sub>PP</sub>  |                                                                                                        |      |      | 150  | mA   |

| Output summer                         | I <sub>OH</sub>  | $V_{DD}$ =1.1 to 5.5 V, $V_{OH}$ = $V_{DD}$ -0.3 V                                                     | -300 |      |      | μA   |

| Output current                        | I <sub>OL</sub>  | $V_{\text{DD}}\text{=}1.1$ to 5.5 V, $V_{\text{OH}}\text{=}0.3$ V                                      | 300  |      |      | μA   |

| Pull-down resistance                  | R <sub>D</sub>   | V <sub>DD</sub> =1.5 V                                                                                 | 0.1  | 0.2  | 0.4  | MΩ   |

### ■ AC Electrical Characteristics

1. Read mode

| <b>Table 6</b><br>(Ta=25°C, V <sub>DD</sub> =1.5 V |                  |      |      |           | ( <sub>22</sub> -1.5.\/) |

|----------------------------------------------------|------------------|------|------|-----------|--------------------------|

| Γ                                                  |                  |      | (10  | 1–20 O, V | 00-1.3 V)                |

| Parameter                                          | Symbol           | Min. | Тур. | Max.      | Unit                     |

| RST hold time                                      | t <sub>RH</sub>  | 5.0  |      |           | μS                       |

| Read cycle time                                    | t <sub>RC</sub>  | 2.0  |      |           | μS                       |

| CLK hold time                                      | t <sub>CH</sub>  | 5.0  |      |           | μS                       |

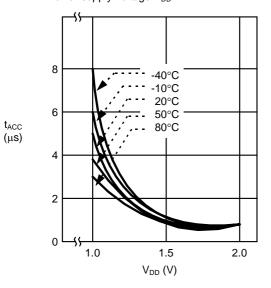

| Access time                                        | t <sub>ACC</sub> |      |      | 5.0       | μs                       |

| CE/PE setup time                                   | t <sub>CES</sub> | 2.0  |      |           | μS                       |

| RST setup time                                     | t <sub>RS</sub>  | 5.0  |      |           | μS                       |

| CLK setup time                                     | t <sub>cs</sub>  | 5.0  |      |           | μS                       |

| CE access time                                     | t <sub>CE</sub>  |      |      | 5.0       | μS                       |

| Output disable time                                | t <sub>WZ</sub>  |      |      | 500       | ns                       |

| CLK and RST inhibit time                           | t <sub>CRI</sub> |      |      | 500       | ns                       |

Load : 60 pF

### 2. Write mode

### Table 7

|                            | Table /          |      |                       |                        |                        |

|----------------------------|------------------|------|-----------------------|------------------------|------------------------|

|                            |                  | (Ta= | =25°C, V <sub>D</sub> | <sub>D</sub> =5.0 V, V | V <sub>PP</sub> =21 V) |

| Parameter                  | Symbol           | Min. | Тур.                  | Max.                   | Unit                   |

| CE-data setup time         | t <sub>CDS</sub> | 0.5  |                       |                        | μS                     |

| Data setup time            | t <sub>DS</sub>  | 0.5  |                       |                        | μS                     |

| Data hold time             | t <sub>DH</sub>  | 0    | _                     |                        | μS                     |

| CE-data hold time          | t <sub>CDH</sub> | 2.0  | _                     |                        | μS                     |

| V <sub>PP</sub> rise time  | tr               | 20   | _                     |                        | μS                     |

| Program pulse width        | t <sub>PW</sub>  | 8.0  |                       | _                      | ms                     |

| V <sub>PP</sub> rise slope | $\Delta V_{PP}$  |      |                       | 4                      | V/µs                   |

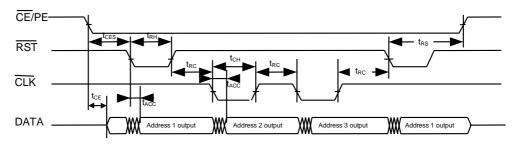

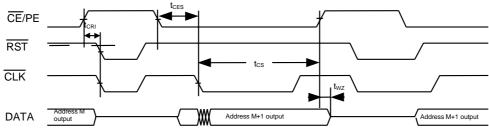

#### Read Mode Operation

By setting the  $\overline{\text{CE}/\text{PE}}$  terminal to "L" level, the S-2100R enters the read mode. \*<sup>1</sup> Next, adding an RST pulse causes the contents of the memory bit of address 1 to be output at the DATA terminal; the rising of the RST pulse latches the data and stabilizes it. \*<sup>2</sup> Reading of addresses from 2 to 64 can be done by adding a CLK pulse sequentially after reading address 1. \*<sup>3</sup> As soon as address 64 has been read, the COUNTER OUT terminal outputs "H" level. When it finishes reading address 64, it does not accept any more CLK pulses and the counter does not operate. The data of address 64 is maintained till address 1 is read by the RST pulse.

Figure 3 Read mode timing

- <sup>\*1</sup> When both the CLK and RST terminals are at "H" level.

- <sup>\*2</sup> When the RST terminal is at "L" level, the latch is transparent and the data is recognized by the rising of the RST pulse.

- <sup>\*3</sup> Data read by the CLK pulse is latched at its rising.

#### Counter Hold Mode Operation

By setting the  $\overline{CE}/PE$  terminal to "H" level, the S-2100R enters the counter hold mode and the DATA terminal becomes high impedance.

In counter hold mode, the  $\overline{\text{CLK}}$  and  $\overline{\text{RST}}$  pulses which fall while the  $\overline{\text{CE}}/\text{PE}$  terminal is at "H" level are recognized to be invalid and there is no change in counter and data output. When the  $\overline{\text{CE}}/\text{PE}$  terminal is set to "L" level again, it returns to the condition in which it was before the counter hold mode.

Figure 4 Counter hold mode timing

\*<sup>4</sup> When both the CLK and RST terminals are at "H" level.

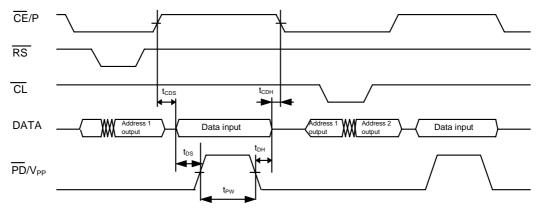

#### Program Mode Operation

By setting the  $\overline{CE}/PE$  terminal to "H" level, the S-2100R enters the counter hold mode and at the same time enters the program mode. \*<sup>5</sup>

Writing is done in program mode after selecting the address in read mode. \*<sup>6</sup> Select the address, and supply "H" level to the  $\overline{\text{CE}}/\text{PE}$  terminal and "L" level to the DATA terminal, with the writing pulse V<sub>PP</sub> being supplied to the  $\overline{P_D}/V_{PP}$  terminal. "L" level can be written into the selected address only once. \*<sup>7</sup> \*<sup>8</sup>

If you coutinue writing from address 1 to 64, the output of the COUNTER OUT terminal goes to "H" level, just like in the read mode, and no more CLK pulses or writing pulses in program mode can be accepted.

Figure 5 Program mode timing

- <sup>\*5</sup> In program mode, operate at VDD=5.0 V to assure reliability of the data writing.

- \*6 The selection of addresses is possible only in read mode. Address 1 is selected by RST pulses and writing proceeds sequentially from address 1 by CLK pulse.

- \*7 All the memories are initially at "H" level, so writing into "L" can be done. When data is at "H" level, writing voltage cannot be supplied to the memory.

- \*<sup>8</sup> Address 1 is selected again by the RST pulse. The addresses which are not written to "L" level are at "H" level, so writing "L" level in these addresses is possible.

#### Input Priority

In read mode, priority is given to either the  $\overline{\text{CLK}}$  or  $\overline{\text{RST}}$  terminal, whichever is entered first. Whichever pulse is input earlier is recognized to be valid from the rising till the end of the operation. If the pulse input later is at "L" level, the signal is ignored, even though the effective pulse input earlier rises. \*<sup>9</sup>

If the CLK and RST pulses are input, the mode shifts from read mode to counter hold mode when both the CLK and the RST terminals go to "H" level. \*<sup>10</sup>

If the  $\overline{\text{CLK}}$  and  $\overline{\text{RST}}$  pulses which are input in the counter hold mode are still at "L" level after setting the  $\overline{\text{CE}}/\text{PE}$  terminal to "L" level, these  $\overline{\text{CLK}}$  and  $\overline{\text{RST}}$  terminals are ignored. The mode shifts to read mode and data which is held before the shift is output at the DATA terminal. \*<sup>11</sup>

In program mode, inputting the DATA terminal before the  $\overline{CE}/PE$  terminal goes to "H" level is prohibited. Also, charging the writing voltage from the P<sub>D</sub>/V<sub>PP</sub> terminal is prohibited when the  $\overline{CE}/PE$  terminal is at "L" level. In program mode, input to the DATA terminal muse be decided before charging the writing voltage. \*<sup>12</sup>

- <sup>\*9</sup> Input of the CLK and RST pulses is not recognized as valid unless both pulses are input at "H" level.

- \*<sup>10</sup> The counter hold mode is entered when reading of the CLK and RST pulses has been finished and DATA output has been stabilized.

- \*11 No more CLK or RST pulses are accepted unless both the CLK and RST terminals are at "H" level.

- \*<sup>12</sup> If data input is changed while writing voltage is supplied, the S-2100R does not accept the changed data.

#### Notes

Memory should not be accessed for at least 10  $\mu s$  after voltage is supplied and goes to  $V_{\text{DD}}.$

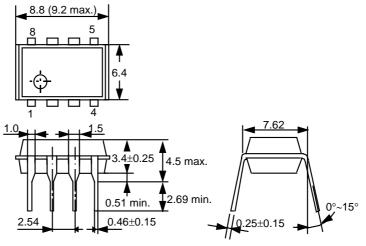

## Dimensions

1. 8-pin DIP

Unit:mm

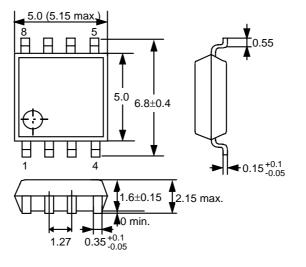

2. 8-pin SOP

Unit: mm

Figure 7

# 64-bit FUSE ROM S-2100R

#### Characteristics

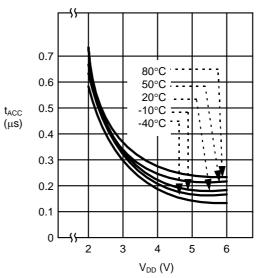

2. Access time  $t_{ACC}$ -Power supply voltage  $V_{DD}$

Access time t<sub>ACC</sub>-Power supply voltage V<sub>DD</sub>