Order this document by MC68HC705V12/D Rev. 3.0

**Advance Information**

This document contains information on a new product. Specifications and information herein are subject to change without notice.

## **Advance Information**

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

© Motorola, Inc., 1999

Advance Information MC68HC705V12 — Rev. 3.0

2 MOTOROLA

# **List of Sections**

| Section 1. General Description                           |

|----------------------------------------------------------|

| Section 2. Memory Map                                    |

| Section 3. Central Processor Unit (CPU) 49               |

| Section 4. Interrupts                                    |

| Section 5. Resets                                        |

| Section 6. Low-Power Modes                               |

| Section 7. Parallel Input/Output (I/O) 81                |

| Section 8. Core Timer 87                                 |

| Section 9. 16-Bit Timer                                  |

| Section 10. Serial Peripheral Interface (SPI) 101        |

| Section 11. Pulse Width Modulators (PWMs) 113            |

| Section 12. EPROM and EEPROM                             |

| Section 13. Analog-to-Digital (A/D) Converter 131        |

| Section 14. Byte Data Link Controller – Digital (BDLC-D) |

| Section 15. Gauge Drivers                                |

| Section 16. Instruction Set                              |

| Section 17. Electrical Specifications                    |

| Section 18. Mechanical Specifications 243                |

| Section 19. Ordering Information 245                     |

MC68HC705V12 — Rev. 3.0

# List of Sections

# **Table of Contents**

## **Section 1. General Description**

| 1.1            | Contents                                                         |

|----------------|------------------------------------------------------------------|

| 1.2            | Introduction                                                     |

| 1.3            | Features                                                         |

| 1.4            | MCU Structure                                                    |

| 1.5            | Programmable Mask Options                                        |

| 1.6<br>1.6.1   | Operating Modes                                                  |

| 1.6.2          | Bootloader Mode                                                  |

| 1.7            | Functional Pin Descriptions                                      |

| 1.7.1          | V <sub>DD</sub> and V <sub>SSD</sub>                             |

| 1.7.2<br>1.7.3 | V <sub>SSA</sub>                                                 |

| 1.7.4          | $V_{REFH}$ and $V_{REFL}$                                        |

| 1.7.5          | OSC1 and OSC229                                                  |

| 1.7.5.         |                                                                  |

| 1.7.5.2        |                                                                  |

| 1.7.5.3        |                                                                  |

| 1.7.6          | RESET                                                            |

| 1.7.7          | ĪRQ/V <sub>PP</sub> 31                                           |

| 1.7.8          | PA0-PA6                                                          |

| 1.7.9          | PB0–PB3 (SPI Pins), PB4/PWMA, PB5/PWMB, PB6/TCMP, and PB7/TCAP32 |

| 1.7.10         |                                                                  |

| 1.7.11         |                                                                  |

| 1.7.12         |                                                                  |

| 1.7.13         |                                                                  |

| 1.7.14         |                                                                  |

| 1.7.15         | 100                                                              |

|                |                                                                  |

# **Table of Contents**

|                    | 1.7.16       | S V <sub>SSG</sub>                                                        |

|--------------------|--------------|---------------------------------------------------------------------------|

|                    | 1.7.17       | OVICE                                                                     |

|                    | 1.7.18       | MAJA(B)1+, MAJA(B)1-, MAJA(B)2+,<br>and MAJA(B)2                          |

|                    | 1.7.19       | MINA(B,C,D)1, MINA(B,C,D)2+, and MINA(B,C,D)234                           |

|                    | 1.8          | Power Supply Pin Connections35                                            |

|                    | 1.9          | Decoupling Recommendations35                                              |

|                    | 1.9.1        | V <sub>DD</sub> to V <sub>SSD</sub> — MCU Internal Digital                |

|                    | 100          | Power Decoupling                                                          |

|                    | 1.9.2        | V <sub>CCA</sub> to V <sub>SSA</sub> — Analog Subsystem Power Supply Pins |

|                    |              |                                                                           |

|                    |              | Section 2. Memory Map                                                     |

|                    | 2.1          | Contents                                                                  |

|                    | 2.2          | Introduction                                                              |

|                    | 2.3          | I/O and Control Registers                                                 |

|                    | 2.4          | RAM47                                                                     |

|                    | 2.5          | Boot ROM                                                                  |

|                    | 2.6          | EPROM                                                                     |

|                    | 2.7          | EEPROM                                                                    |

|                    | 2.8          | Miscellaneous Register48                                                  |

|                    |              | Section 3. Central Processor Unit (CPU)                                   |

|                    | 3.1          | Contents                                                                  |

|                    | 3.2          | Introduction                                                              |

|                    |              |                                                                           |

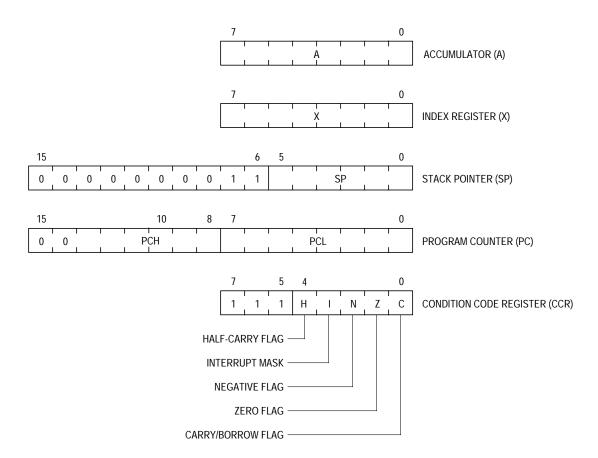

|                    | 3.3<br>3.3.1 | CPU Registers                                                             |

|                    | 3.3.2        | Index Register                                                            |

|                    | 3.3.3        | Stack Pointer51                                                           |

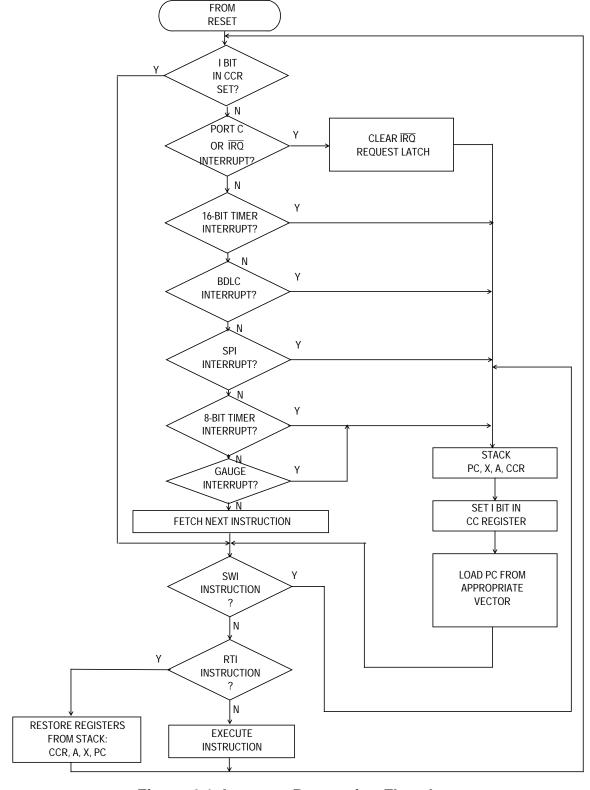

|                    | 3.3.4        | Program Counter                                                           |

|                    | 3.3.5        | Condition Code Register53                                                 |

|                    | 3.4          | Arithmetic/Logic Unit54                                                   |

| vance Information  |              | MC68HC705V12 — Rev. 3.0                                                   |

| variou information |              | WICOUTIOT 03 V 12 — 1/eV. 3.0                                             |

# **Section 4. Interrupts**

| 4.1                   | Contents                                   |  |  |

|-----------------------|--------------------------------------------|--|--|

| 4.2                   | Introduction                               |  |  |

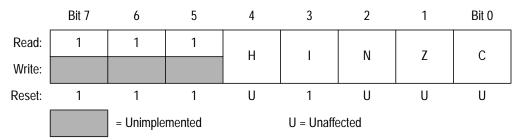

| 4.3                   | CPU Interrupt Processing56                 |  |  |

| 4.4                   | Reset Interrupt Sequence59                 |  |  |

| 4.5                   | Software Interrupt (SWI)59                 |  |  |

| 4.6                   | Hardware Interrupts                        |  |  |

| 4.7<br>4.7.1<br>4.7.2 | External Interrupt (IRQ)                   |  |  |

| 4.8                   | 16-Bit Timer Interrupt                     |  |  |

| 4.9                   | BDLC Interrupt                             |  |  |

| 4.10                  | SPI Interrupt                              |  |  |

| 4.11                  | 8-Bit Timer Interrupt                      |  |  |

| 4.12                  | Gauge Synchronize Interrupt                |  |  |

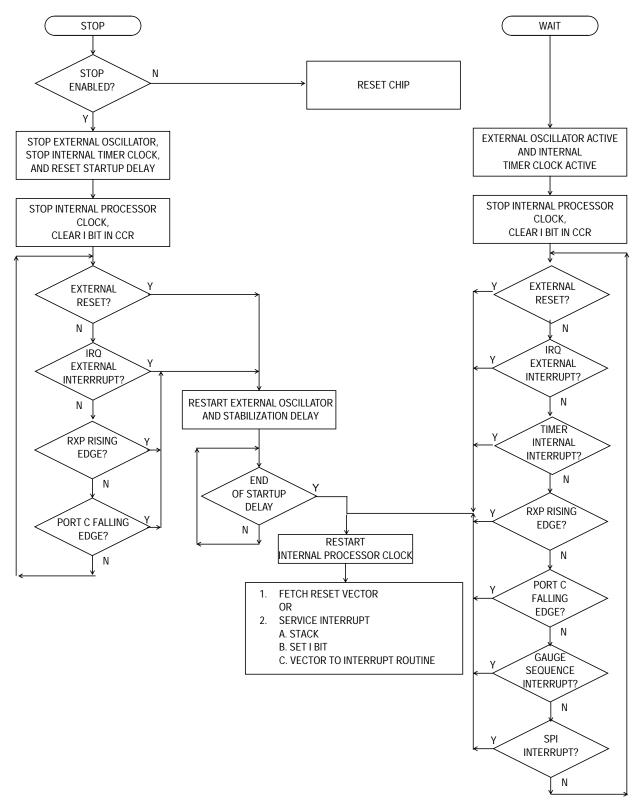

| 4.13                  | Stop Mode and Wait Mode                    |  |  |

| Section 5. Resets     |                                            |  |  |

| 5.1                   | Contents                                   |  |  |

| 5.2                   | Introduction                               |  |  |

| 5.3                   | External Reset (RESET)68                   |  |  |

| 5.4<br>5.4.1          | Internal Resets                            |  |  |

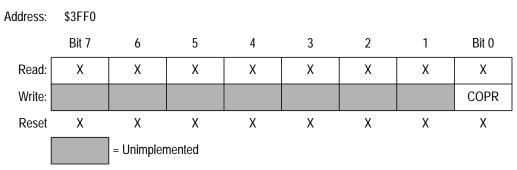

| 5.4.2                 | Computer Operating Properly Reset (COPR)71 |  |  |

| 5.4.2.                | <b>5</b>                                   |  |  |

| 5.4.2.2               | <b>5</b>                                   |  |  |

| 5.4.2.3               | 3 1                                        |  |  |

| 5.4.2.4<br>5.4.2.5    | 3                                          |  |  |

| 5.4.2.                | 5 COP Register73 Illegal Address Reset73   |  |  |

| 5.4.4                 | Disabled STOP Instruction Reset            |  |  |

| J                     |                                            |  |  |

MC68HC705V12 — Rev. 3.0

| 5.4.5<br>5.4.6                 | Low-Voltage Reset (LVR)                  |

|--------------------------------|------------------------------------------|

| 00                             | 2717 Operation in Ctop and Train medec   |

|                                | Section 6. Low-Power Modes               |

| 6.1                            | Contents                                 |

| 6.2                            | Introduction                             |

| 6.3                            | STOP Instruction                         |

| 6.4                            | Stop Mode76                              |

| 6.5                            | WAIT Instruction                         |

| 6.6                            | Data-Retention Mode                      |

|                                | Section 7. Parallel Input/Output (I/O)   |

| 7.1                            | Contents                                 |

| 7.2                            | Introduction                             |

| 7.3<br>7.3.1<br>7.3.2          | Port A                                   |

| 7.4<br>7.4.1<br>7.4.2          | Port B                                   |

| 7.5<br>7.5.1<br>7.5.2<br>7.5.3 | Port C                                   |

| 7.6                            | Port D                                   |

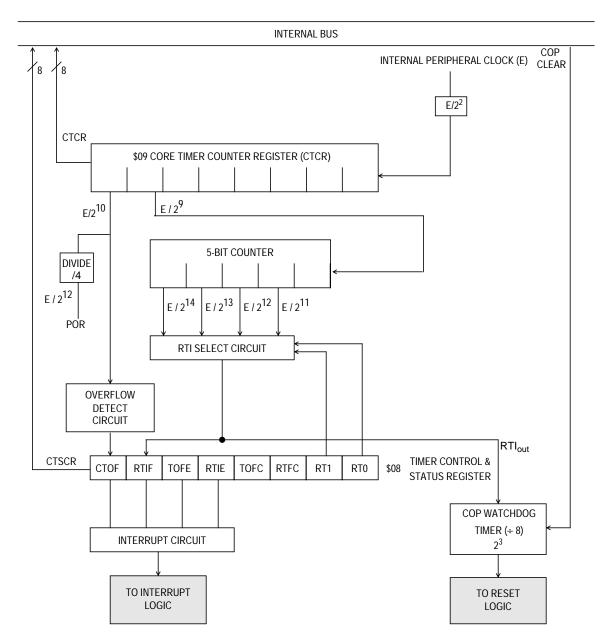

|                                | Section 8. Core Timer                    |

| 8.1                            | Contents                                 |

| 8.2                            | Introduction                             |

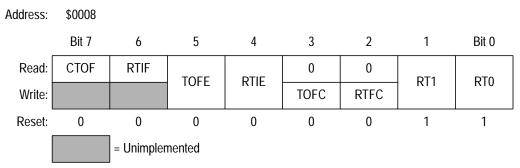

| 8.3                            | Core Timer Status and Control Register89 |

| 8.4                            | Computer Operating Properly (COP) Reset  |

| Advance Information            | MC68HC705V12 — Rev. 3.0                  |

| 8.5              | Core Timer Counter Register                       |

|------------------|---------------------------------------------------|

| 8.6              | Core Timer during Wait Mode                       |

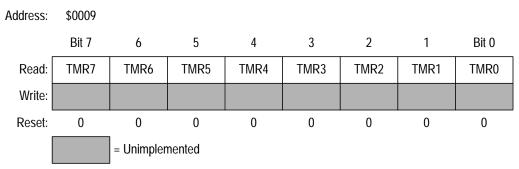

|                  | Section 9. 16-Bit Timer                           |

| 9.1              | Contents                                          |

| 9.2              | Introduction93                                    |

| 9.3              | Timer Counter Registers \$18-\$19 and \$1A-\$1B94 |

| 9.4              | Output Compare Register \$16-\$1796               |

| 9.5              | Input Capture Register \$14-\$15                  |

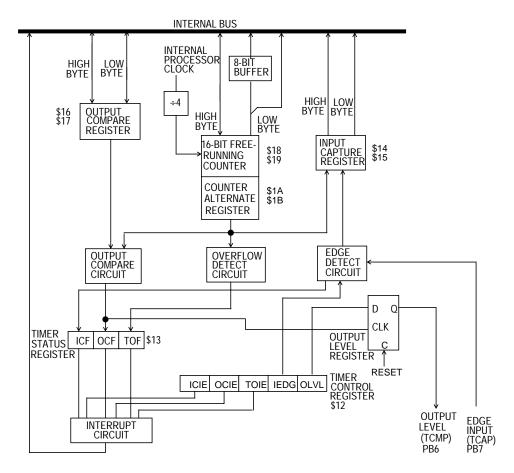

| 9.6              | 16-Bit Timer Control Register                     |

| 9.7              | 16-Bit Timer Status Register                      |

| 9.8              | 16-Bit Timer during Wait Mode                     |

| 9.9              | 16-Bit Timer during Stop Mode                     |

|                  | Section 10. Serial Peripheral Interface (SPI)     |

| 10.1             | Contents                                          |

| 10.2             | Introduction                                      |

| 10.3             | Features                                          |

| 10.4             | SPI Signal Description                            |

| 10.4.1           |                                                   |

| 10.4.2<br>10.4.3 | ,                                                 |

| 10.4.4           | ,                                                 |

| 10.5             | SPI Functional Description                        |

| 10.6             | SPI Registers                                     |

| 10.6.1           |                                                   |

| 10.6.2<br>10.6.3 | · · · · · · · · · · · · · · · · · · ·             |

|                  | · · · · · · · · · · · · · · · · · · ·             |

| 10.7             | SPI in Stop Mode                                  |

|                                              | Section 11. Pulse Width Modulators (PWMs)     |  |  |

|----------------------------------------------|-----------------------------------------------|--|--|

| 11.1                                         | Contents                                      |  |  |

| 11.2                                         | Introduction                                  |  |  |

| 11.3                                         | PWM Functional Description                    |  |  |

| 11.4<br>11.4.1<br>11.4.2<br>11.4.3<br>11.4.4 | PWMA Data Register                            |  |  |

| 11.5                                         | PWMs during Wait Mode                         |  |  |

| 11.6                                         | PWMs during Stop Mode                         |  |  |

| 11.7                                         | PWMs during Reset                             |  |  |

| Section 12. EPROM and EEPROM                 |                                               |  |  |

| 12.1                                         | Contents                                      |  |  |

| 12.2                                         | Introduction                                  |  |  |

| 12.3                                         | EPROM Bootloader122                           |  |  |

| 12.4                                         | Bootloader Functions                          |  |  |

| 12.5                                         | EPROM Programming                             |  |  |

| 12.6                                         | EPROM Programming Register                    |  |  |

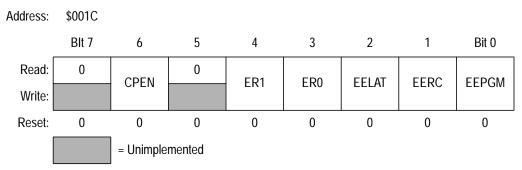

| 12.7                                         | Mask Option Register                          |  |  |

| 12.8                                         | EEPROM Programming Register                   |  |  |

| 12.9                                         | EEPROM Programming/Erasing Procedure129       |  |  |

| 12.10                                        | Operation in Stop Mode and Wait Mode130       |  |  |

|                                              | Section 13. Analog-to-Digital (A/D) Converter |  |  |

| 13.1                                         | Contents                                      |  |  |

| 13.2                                         | Introduction                                  |  |  |

Advance Information

MC68HC705V12 — Rev. 3.0

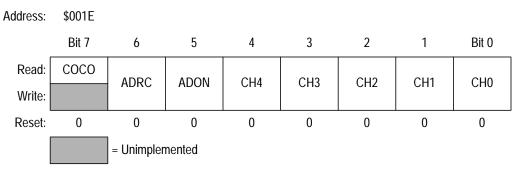

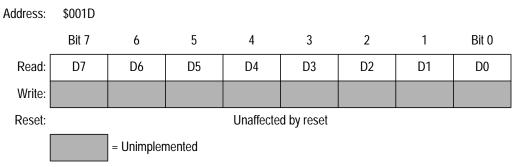

| 13.3<br>13.3.1<br>13.3.2<br>13.3.3<br>13.3.4<br>13.4.1<br>13.4.2<br>13.4.3<br>13.5<br>13.6 | Ratiometric Conversion  V <sub>REFH</sub> and V <sub>REFL</sub> .  Accuracy and Precision.  Conversion Process  Digital Section.  Conversion Times  Internal and Master Oscillators | 132<br>132<br>132<br>133<br>133<br>133<br>133 |

|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|                                                                                            | -                                                                                                                                                                                   |                                               |

| 13.7                                                                                       | A/D during Wait Mode                                                                                                                                                                |                                               |

| 13.8                                                                                       | A/D during Stop Mode                                                                                                                                                                | 136                                           |

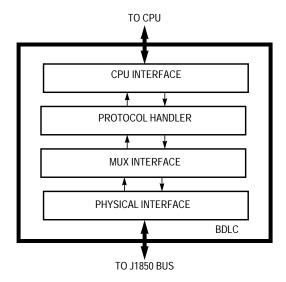

| <b>Sect</b> 14.1                                                                           | ion 14. Byte Data Link Controller – Digital (BDLC–Contents                                                                                                                          | -                                             |

|                                                                                            |                                                                                                                                                                                     |                                               |

| 14.2                                                                                       | Introduction                                                                                                                                                                        |                                               |

| 14.3                                                                                       | Features                                                                                                                                                                            | 139                                           |

| 14.4                                                                                       | Functional Description                                                                                                                                                              |                                               |

| 14.4.1                                                                                     | promise                                                                                                                                                                             |                                               |

| 14.4.1                                                                                     |                                                                                                                                                                                     |                                               |

| 14.4.1<br>14.4.1                                                                           |                                                                                                                                                                                     |                                               |

| 14.4.1                                                                                     |                                                                                                                                                                                     |                                               |

| 14.4.1                                                                                     |                                                                                                                                                                                     |                                               |

| 14.4.1                                                                                     |                                                                                                                                                                                     |                                               |

| 14.4.1                                                                                     | .7 Analog Loopback Mode                                                                                                                                                             | 145                                           |

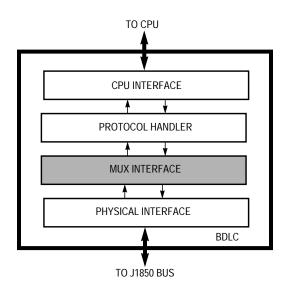

| 14.5                                                                                       | BDLC MUX Interface                                                                                                                                                                  | 145                                           |

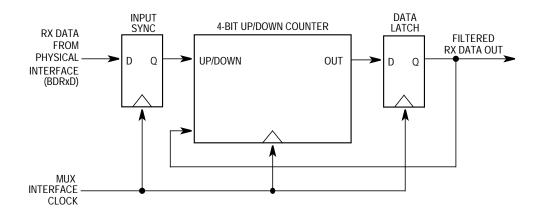

| 14.5.1                                                                                     | Rx Digital Filter                                                                                                                                                                   | 146                                           |

| 14.5.1                                                                                     | E Principal Control                                                                                                                                                                 |                                               |

| 14.5.1                                                                                     | ·                                                                                                                                                                                   |                                               |

| 14.5.2<br>14.5.3                                                                           |                                                                                                                                                                                     |                                               |

| 14.5.4                                                                                     |                                                                                                                                                                                     |                                               |

|                                                                                            | 2. 2. 2. 2. 2. 2. 2. 2. 2. 2. 2. 2. 2. 2                                                                                                                                            |                                               |

# **Table of Contents**

14.5.5

|                     | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

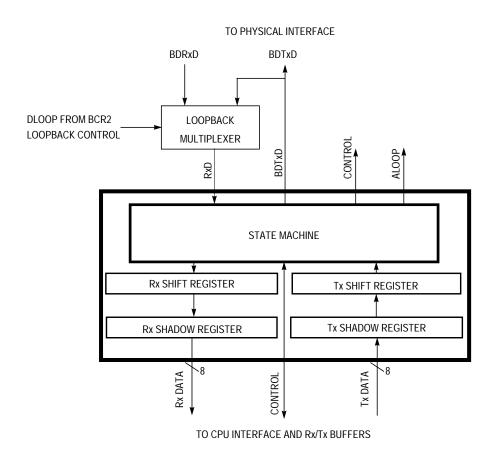

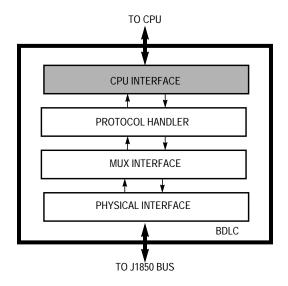

|                     | 14.6       BDLC Protocol Handler       160         14.6.1       Protocol Architecture       161         14.6.2       Rx and Tx Shift Registers       162         14.6.3       Rx and Tx Shadow Registers       162         14.6.4       Digital Loopback Multiplexer       162         14.6.5       State Machine       162         14.6.5.1       4X Mode       163         14.6.5.2       Receiving a Message in Block Mode       163         14.6.5.3       Transmitting a Message in Block Mode       163         14.6.5.4       J1850 Bus Errors       163         14.6.5.5       Summary       165         14.7       BDLC CPU Interface       166 |

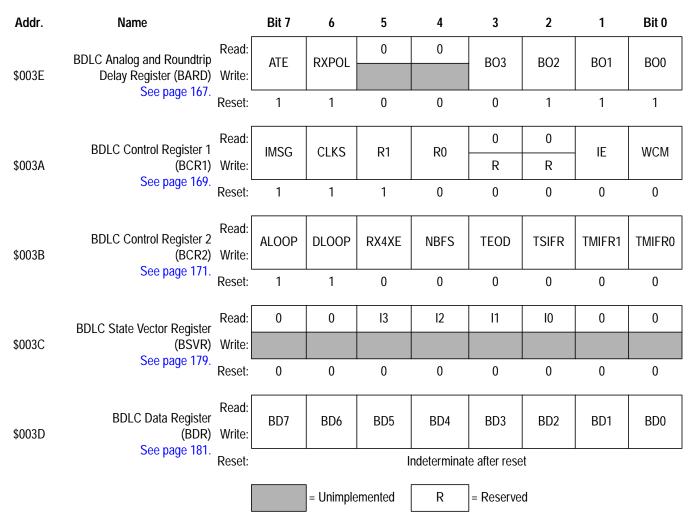

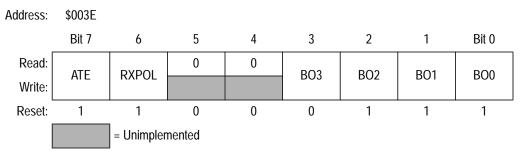

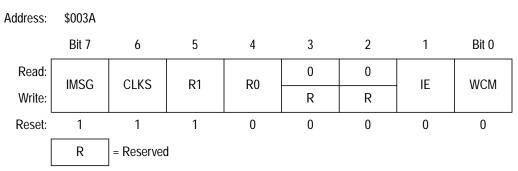

|                     | 14.7 BDLC CPO Interface.16614.7.1 BDLC Analog and Roundtrip Delay.16714.7.2 BDLC Control Register 1.16914.7.3 BDLC Control Register 2.17114.7.4 BDLC State Vector Register17914.7.5 BDLC Data Register181                                                                                                                                                                                                                                                                                                                                                                                                                                                |

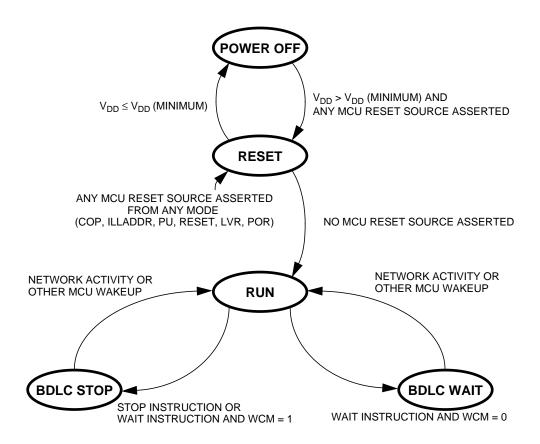

|                     | 14.8 Low-Power Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                     | Section 15. Gauge Drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                     | 15.1 Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                     | 15.2 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

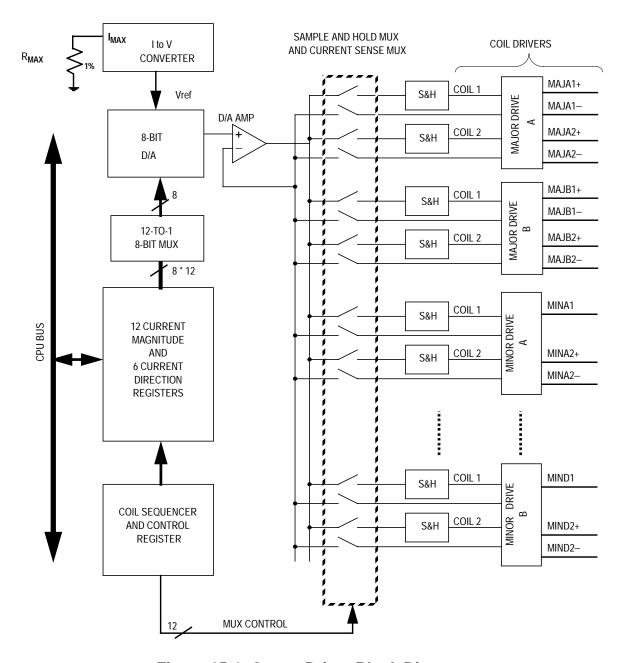

|                     | 15.3 Gauge System Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                     | 15.4 Coil Drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                     | 15.5 Technical Note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                     | 15.6Gauge Driver Control Registers.19115.6.1Gauge Enable Register.19115.6.2Current Magnitude Registers.19315.6.3Current Direction Registers.19515.6.3.1Current Direction Register for Major A.19615.6.3.2Current Direction Register for Major B.196                                                                                                                                                                                                                                                                                                                                                                                                      |

| Advance Information | MC68HC705V12 — Rev. 3.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 15.6.3.3 Current Direction Register for Minor A    |

|----------------------------------------------------|

| 15.6.3.4 Current Direction Register for Minor B19  |

| 15.6.3.5 Current Direction Register for Minor C198 |

| 15.6.3.6 Current Direction Register for Minor D    |

| 15.7 Coil Sequencer and Control                    |

| 15.7.1 Scanning Sequence Description               |

| 15.7.1.1 Automatic Mode                            |

| 15.7.1.2 Manual Mode                               |

| 15.7.2 Scan Status and Control Register202         |

| 15.8 Mechanism Diagram204                          |

| 15.9 Gauge Power Supply                            |

| 15.10 Gauge Regulator Accuracy200                  |

| 15.11 Coil Current Accuracy                        |

| 15.12 External Component Considerations            |

| 15.12.1 Minimum Voltage Operation                  |

| 15.12.2 Power Dissipation                          |

| 15.12.3 Coil Inductance Limits                     |

| 15.13 Operation in Wait Mode                       |

| 15.14 Operation in Stop Mode                       |

| Section 16. Instruction Set                        |

| 16.1 Contents                                      |

| 16.2 Introduction                                  |

| 16.3 Addressing Modes                              |

| 16.3.1 Inherent213                                 |

| 16.3.2 Immediate                                   |

| 16.3.3 Direct                                      |

| 16.3.4 Extended                                    |

| 16.3.5 Indexed, No Offset                          |

| 16.3.6 Indexed, 8-Bit Offset                       |

| 16.3.7 Indexed,16-Bit Offset                       |

| 16.3.8 Relative                                    |

# **Table of Contents**

| 16.4.1<br>16.4.2<br>16.4.3<br>16.4.4<br>16.4.5 | Read-Modify-Write Instructions                                 |

|------------------------------------------------|----------------------------------------------------------------|

| 16.5                                           | Instruction Set Summary222                                     |

|                                                | Section 17. Electrical Specifications                          |

| 17.1                                           | Contents                                                       |

| 17.2                                           | Maximum Ratings230                                             |

| 17.3                                           | Operating Temperature Range231                                 |

| 17.4                                           | Thermal Characteristics                                        |

| 17.5                                           | Power Considerations                                           |

| 17.6                                           | DC Electrical Characteristics                                  |

| 17.7                                           | Control Timing                                                 |

| 17.8                                           | A/D Converter Characteristics                                  |

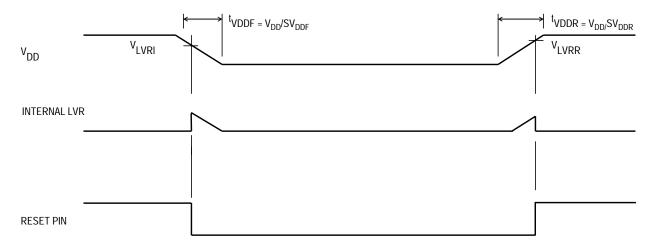

| 17.9                                           | LVR Timing Diagram237                                          |

| 17.10                                          | Serial Peripheral Interface (SPI) Timing                       |

| 17.11                                          | Gauge Driver Electricals240                                    |

| 17.12                                          | BDLC Transmitter VPW Symbol Timings (BARD) Bits BO[3:0] = 0111 |

| 17.13                                          | BDLC Receiver VPW Symbol Timings (BARD) Bits BO[3:0] = 0111    |

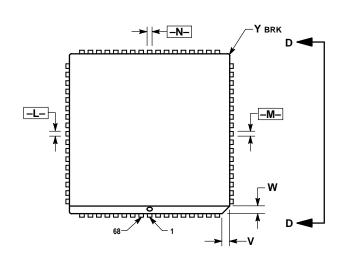

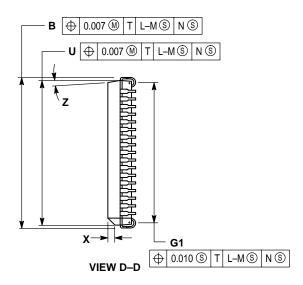

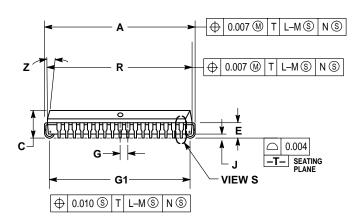

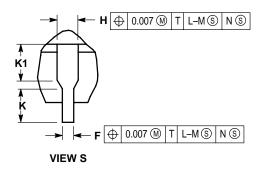

|                                                | Section 18. Mechanical Specifications                          |

| 18.1                                           | Contents                                                       |

| 18.2                                           | Introduction                                                   |

| 18.3                                           | 68-Lead Plastic Leaded Chip Carrier (PLCC)                     |

Advance Information

MC68HC705V12 — Rev. 3.0

# **Section 19. Ordering Information**

| 19.1 | Contents        | .245 |

|------|-----------------|------|

| 19.2 | Introduction    | .245 |

| 19.3 | MC Order Number | .245 |

15

# **Table of Contents**

# **List of Figures**

| Figure | Title                                    | Page |

|--------|------------------------------------------|------|

| 1-1    | MC68HC705V12 Block Diagram               | 26   |

| 1-2    | Pin Assignments (68-Pin PLCC Package)    | 28   |

| 1-3    | Oscillator Connections                   | 30   |

| 1-4    | Supply Decoupling Diagram                | 35   |

| 1-5    | Single-Sided PCB Example                 | 36   |

| 2-1    | MC68HC705V12 Single-Chip Mode Memory Map | 38   |

| 2-2    | MC68HC705V12 I/O Registers Memory Map    | 39   |

| 2-3    | I/O and Control Registers                | 40   |

| 2-4    | Miscellaneous Register (MISC)            | 48   |

| 3-1    | Programming Model                        | 50   |

| 3-2    | Accumulator (A)                          | 51   |

| 3-3    | Index Register (X)                       | 51   |

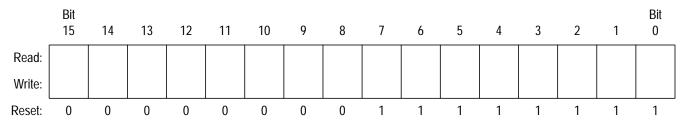

| 3-4    | Stack Pointer (SP)                       | 52   |

| 3-5    | Program Counter (PC)                     | 52   |

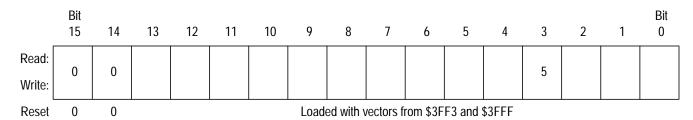

| 3-6    | Condition Code Register (CCR)            | 53   |

| 4-1    | Interrupt Processing Flowchart           | 58   |

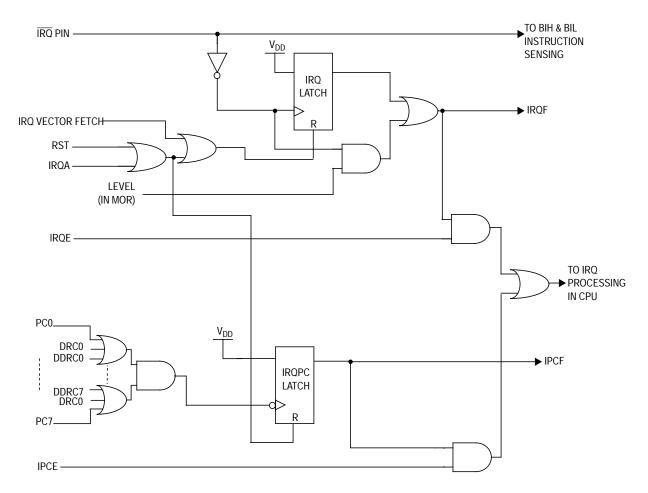

| 4-2    | IRQ Function Block Diagram               | 60   |

| 4-3    | IRQ Status and Control Register (ISCR)   | 62   |

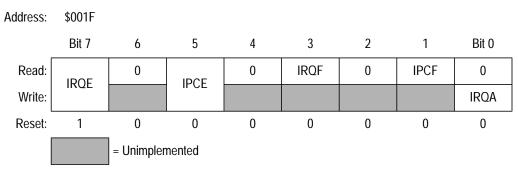

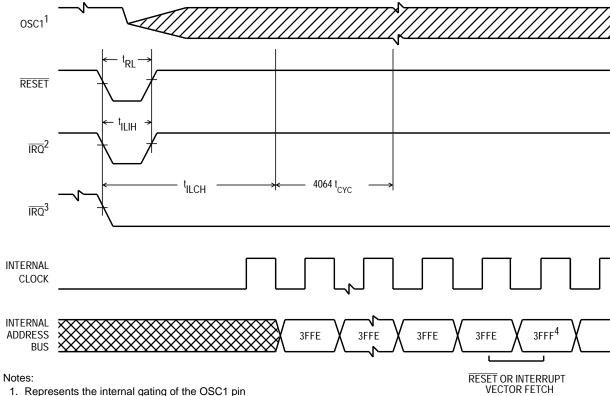

| 4-4    | External Interrupts Timing Diagram       | 64   |

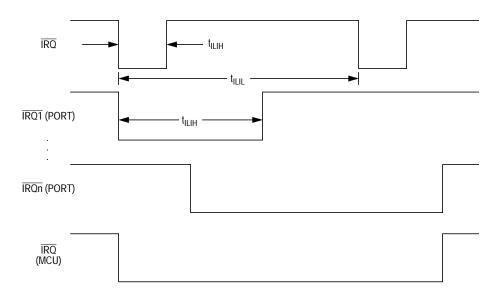

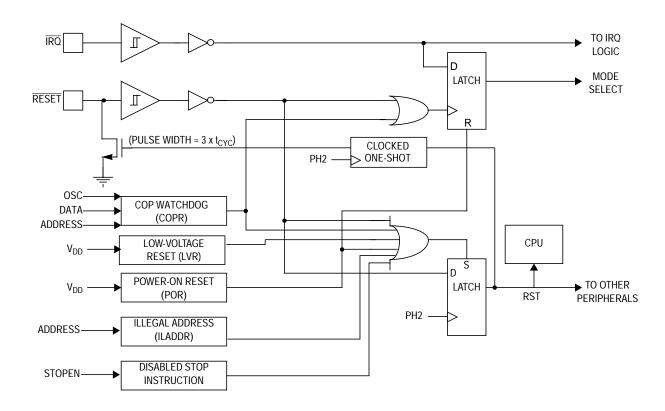

| 5-1    | Reset Block Diagram                      | 68   |

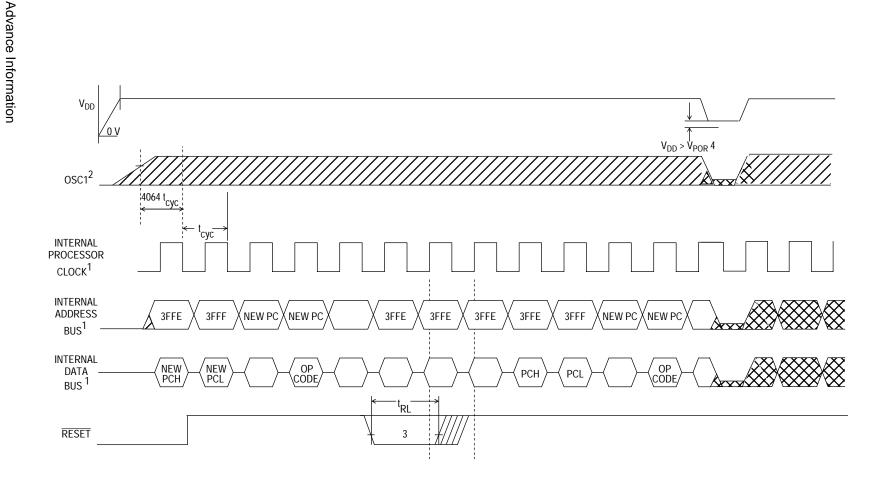

| 5-2    | Reset and POR Timing Diagram             | 70   |

| 5-3    | COP Watchdog Timer Location              | 73   |

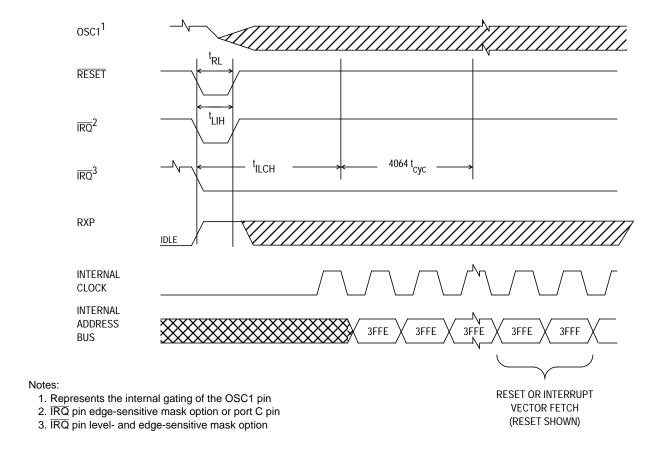

| 6-1    | Stop Recovery Timing Diagram             | 77   |

| 6-2    | Stop/Wait Flowcharts                     | 78   |

|        |                                          |      |

17

| Figure | Title                                                    | Page |

|--------|----------------------------------------------------------|------|

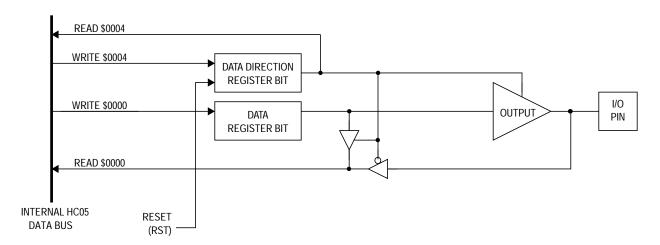

| 7-1    | Port A I/O Circuitry                                     | 82   |

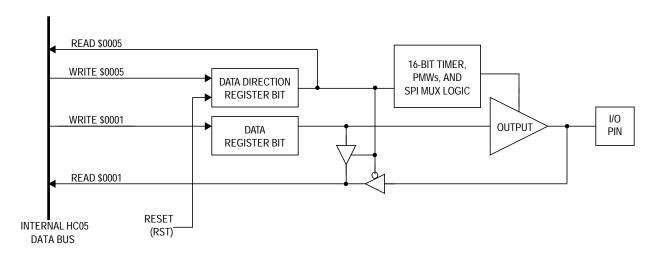

| 7-2    | Port B I/O Circuitry                                     | 83   |

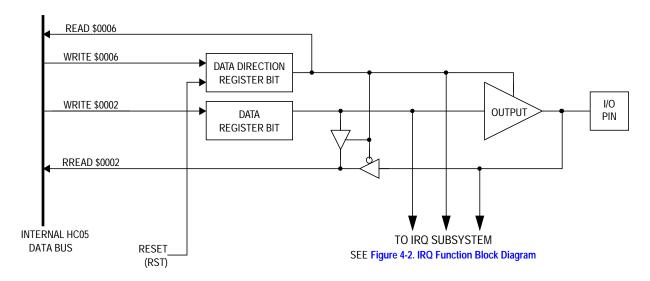

| 7-3    | Port C I/O Circuitry                                     | 84   |

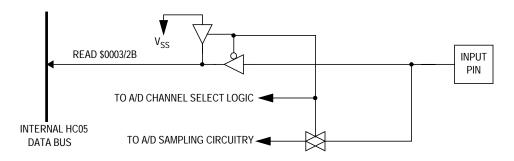

| 7-4    | Port D Circuitry                                         | 86   |

| 8-1    | Core Timer Block Diagram                                 | 88   |

| 8-2    | Core Timer Status and Control Register (CTSCR)           | 89   |

| 8-3    | Core Timer Counter Register (CTCR)                       | 92   |

| 9-1    | 16-Bit Timer Block Diagram                               | 94   |

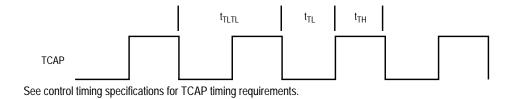

| 9-2    | TCAP Timing                                              | 97   |

| 9-3    | 16- Bit Timer Control Register (TMRCR)                   | 98   |

| 9-4    | Timer Status Register (TMRSR)                            | 99   |

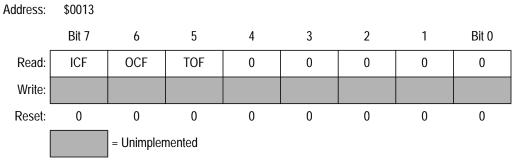

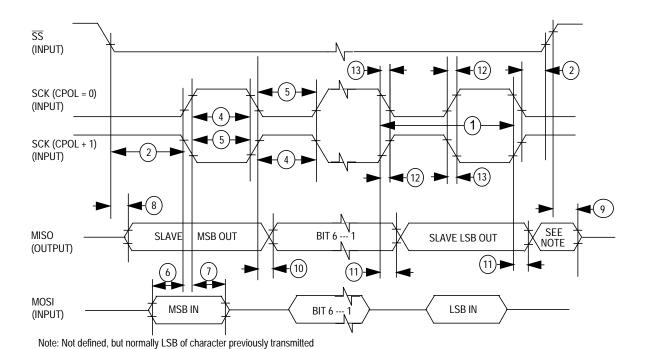

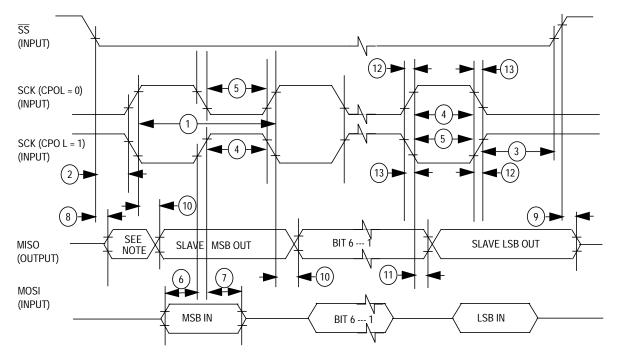

| 10-1   | Data Clock Timing Diagram                                | 103  |

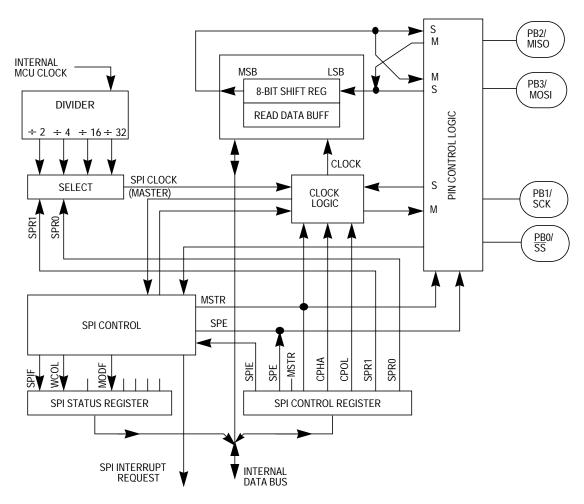

| 10-2   | Serial Peripheral Interface Block Diagram                | 106  |

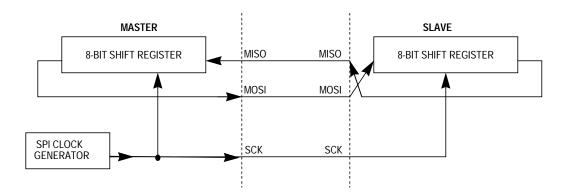

| 10-3   | Serial Peripheral Interface Master-Slave Interconnection | 106  |

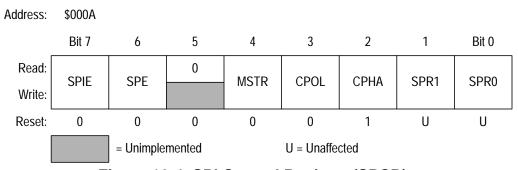

| 10-4   | SPI Control Register (SPCR)                              |      |

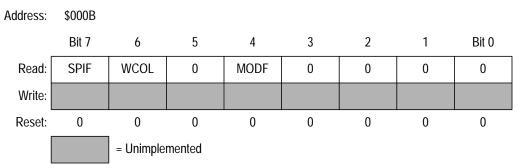

| 10-5   | SPI Status Register (SPSR)                               |      |

| 10-6   | SPI Data Register (SPDR)                                 |      |

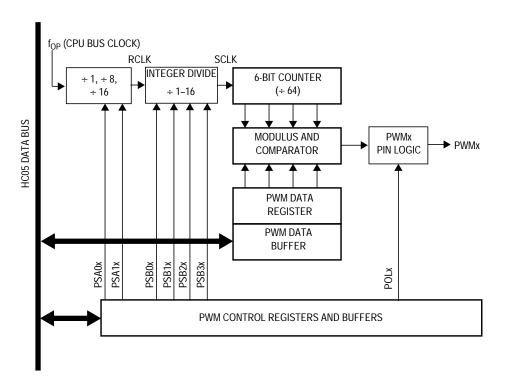

| 11-1   | PWM Block Diagram                                        | 114  |

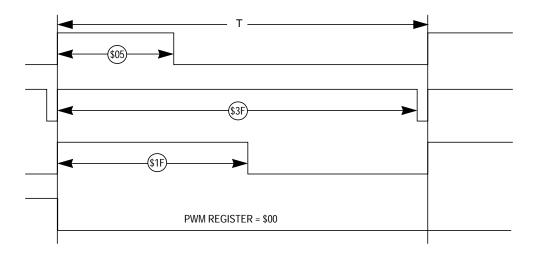

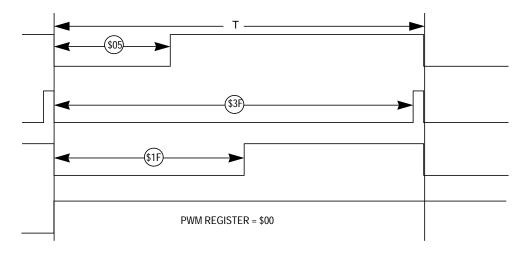

| 11-2   | PWM Waveform Examples (POL = 1)                          | 115  |

| 11-3   | PWM Waveform Examples (POL = 0)                          | 115  |

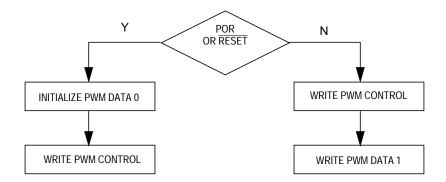

| 11-4   | PWM Write Sequences                                      | 116  |

| 11-5   | PWMA Control Register (PWMAC)                            | 117  |

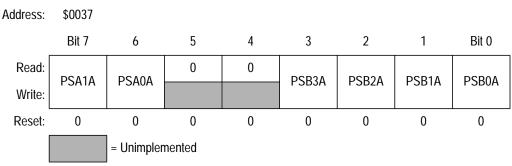

| 11-6   | PWMB Control Register (PWMBC)                            | 118  |

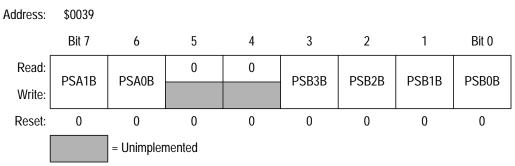

| 11-7   | PWMA Data Register (PWMAD)                               | 119  |

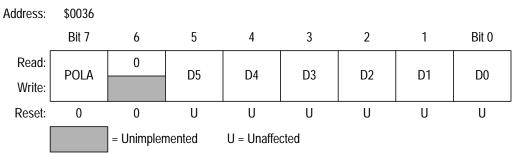

| 11-8   | PWMB Data Register (PWMBD)                               | 119  |

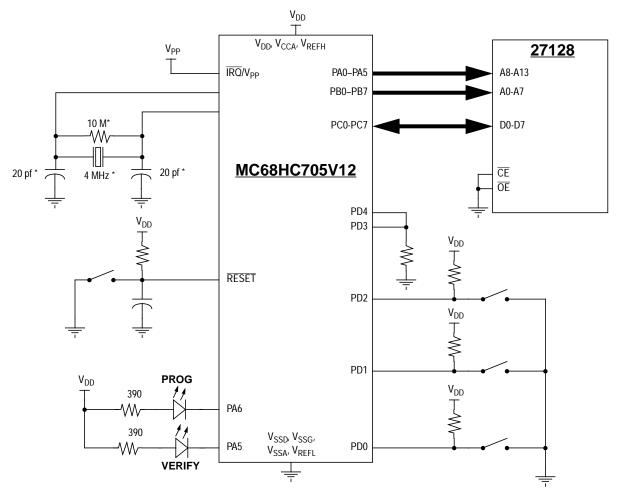

| 12-1   | Bootstrap EPROM Programmer Schematic                     | 123  |

| 12-2   | EPROM Programming Register (EPROG)                       | 124  |

| 12-3   | Mask Option Register (MOR)                               |      |

| 12-4   | EEPROM Programming Register (EEPROG)                     | 127  |

| Figure | Title                                            | Page |

|--------|--------------------------------------------------|------|

| 13-1   | A/D Status and Control Register (ADSCR)          | 134  |

| 13-2   | A/D Data Register (ADDR)                         | 135  |

|        |                                                  |      |

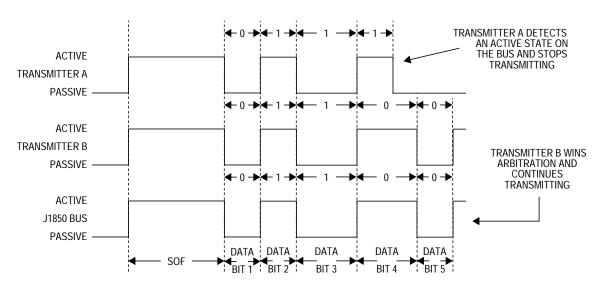

| 14-1   | BDLC Block Diagram                               |      |

| 14-2   | BDLC Input/Output (I/O) Register Summary         |      |

| 14-3   | BDLC Operating Modes State Diagram               |      |

| 14-4   | BDLC Block Diagram                               |      |

| 14-5   | BDLC Rx Digital Filter Block Diagram             |      |

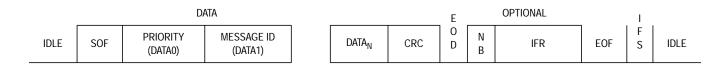

| 14-6   | J1850 Bus Message Format (VPW)                   |      |

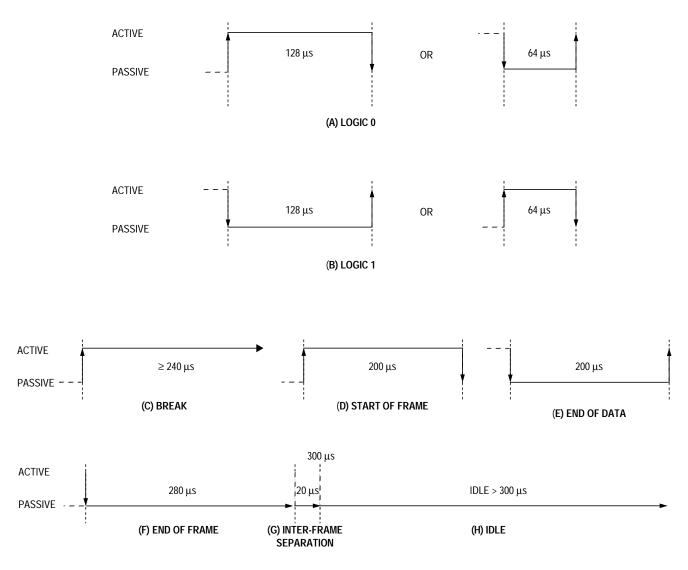

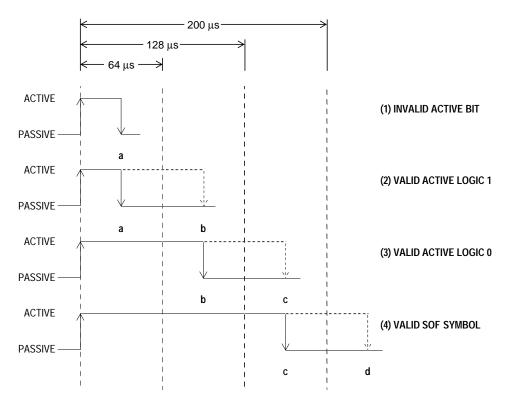

| 14-7   | J1850 VPW Symbols with Nominal Symbol Times      |      |

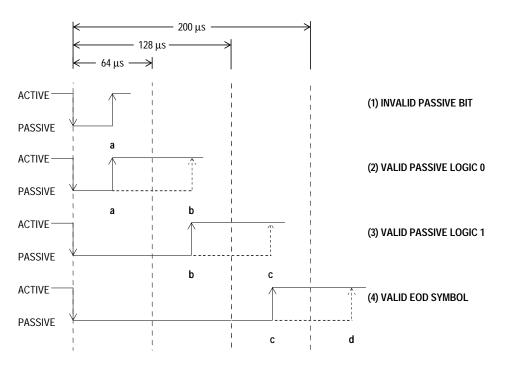

| 14-8   | J1850 VPW Received Passive Symbol Times          | 155  |

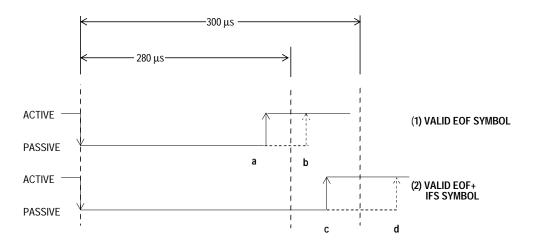

| 14-9   | J1850 VPW Received Passive                       |      |

|        | EOF and IFS Symbol Times                         |      |

| 14-10  | J1850 VPW Received Active Symbol Times           |      |

| 14-11  | J1850 VPW Received BREAK Symbol Times            |      |

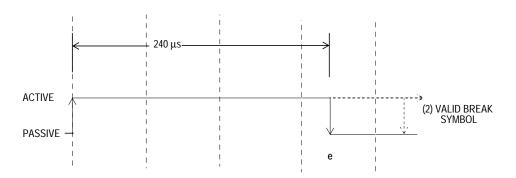

| 14-12  | J1850 VPW Bitwise Arbitrations                   |      |

| 14-13  | BDLC Block Diagram                               |      |

| 14-14  | BDLC Protocol Handler Outline                    |      |

| 14-15  | BDLC Block Diagram                               |      |

| 14-16  | BDLC Analog and Roundtrip Delay Register (BARD). |      |

| 14-17  | BDLC Control Register 1 (BCR1)                   | 169  |

| 14-18  | BDLC Control Register 2 (BCR2)                   |      |

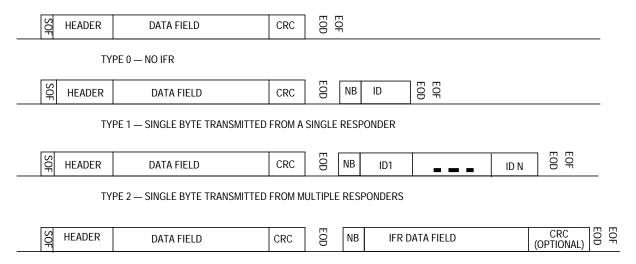

| 14-19  | Types of In-Frame Response (IFR)                 | 175  |

| 14-20  | BDLC State Vector Register (BSVR)                | 179  |

| 14-21  | BDLC Data Register (BDR)                         | 181  |

| 45.4   | Occurs Driver Disell Diserrans                   | 407  |

|        | Gauge Driver Block Diagram                       |      |

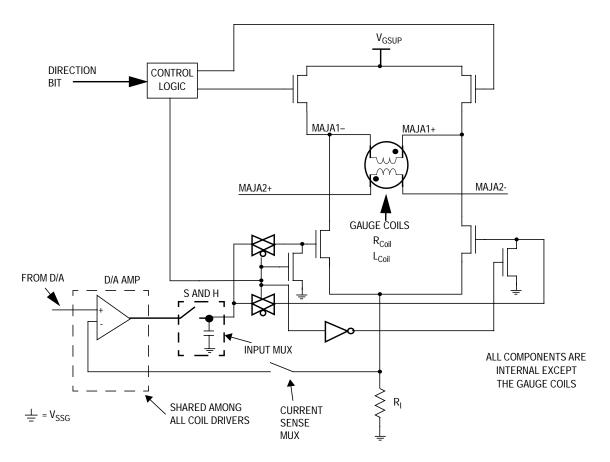

| 15-2   | Full H-Bridge Coil Driver                        |      |

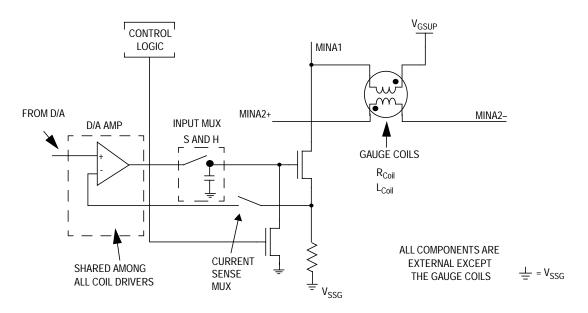

| 15-3   | Half H-Bridge Coil Driver                        |      |

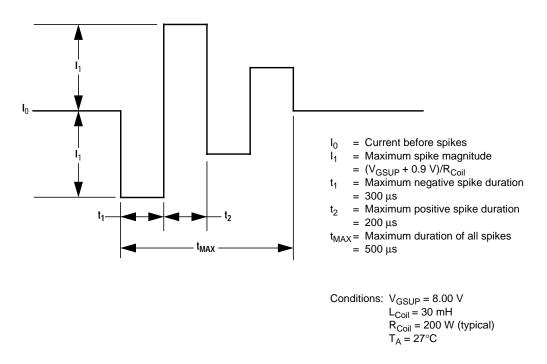

| 15-4   | Specification for Current Spikes                 |      |

| 15-5   | Gauge Enable Register (GER)                      |      |

| 15-6   | Current Magnitude Registers                      |      |

| 15-7   | MAJA Current Direction Register (DMAJA)          |      |

| 15-8   | MAJB Current Direction Register (DMAJB)          |      |

| 15-9   | MINA Current Direction Register (DMINA)          |      |

| 15-10  | MINB Current Direction Register (DMINB)          | 197  |

# List of Figures

| Figure | Title                                       | Page |

|--------|---------------------------------------------|------|

| 15-11  | MINC Current Direction Register (DMINC)     | 198  |

| 15-12  | MIND Current Direction Register (DMIND)     | 198  |

| 15-13  | Scan Status and Control Register (SSCR)     | 202  |

| 15-14  | Sample Gauge Connections to the MC68HC705V1 | 2205 |

| 15-15  | Coil Driver Current Path                    | 207  |

| 17-1   | Stop Recovery Timing Diagram                | 235  |

| 17-2   | LVR Timing Diagram                          | 237  |

| 17-3   | SPI Slave Timing (CPHA = 0)                 | 239  |

| 17-4   | SPI Slave Timing (CPHA = 1)                 | 239  |

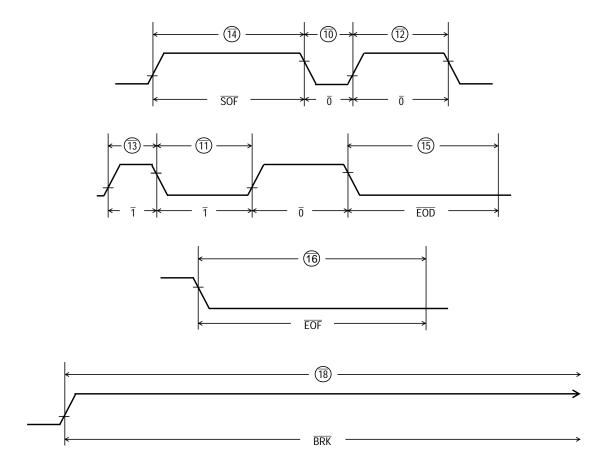

| 17-5   | BDLC Variable Pulse Width Modulation (VPW)  |      |

|        | Symbol Timings                              | 242  |

# **List of Tables**

| Table                   | Title                                                         | Page              |

|-------------------------|---------------------------------------------------------------|-------------------|

| 4-1                     | Vector Address for Interrupts and Reset                       | 57                |

| 5-1                     | COP Watchdog Timer Recommendations                            | 72                |

| 8-1                     | RTI and COP Rates at 2.1 MHz                                  | 90                |

| 10-1                    | Serial Peripheral Rate Selection                              | 108               |

| 11-1                    | PWMA Clock Rates                                              | 117               |

| 11-2                    | PWMB Clock Rates                                              | 118               |

| 12-1                    | Bootloader Functions                                          | 122               |

| 12-2                    | Erase Mode Select                                             | 127               |

| 12-3                    | EEPROM Write/Erase Cycle Reduction                            |                   |

| 13-1                    | A/D Channel Assignments                                       | 135               |

| 14-1                    | BDLC J1850 Bus Error Summary                                  | 165               |

| 14-2                    | BDLC Transceiver Delay                                        | 168               |

| 14-3                    | BDLC Rate Selection                                           | 170               |

| 14-4                    | BDLC Transmit In-Frame Response Control Bit Priority Encoding | 174               |

| 14-5                    | BDLC Interrupt Sources                                        |                   |

| 15-1                    | Coil Scanning Sequencer                                       | 201               |

| 15-2                    | Gauge Module Clock Select Bits                                | 203               |

| 16-1                    | Register/Memory Instructions                                  | 216               |

| 16-2                    | Read-Modify-Write Instructions                                |                   |

| 16-3                    | Jump and Branch Instructions                                  | 219               |

| MC68HC705V12 — Rev. 3.0 | Ac                                                            | vance Information |

# List of Tables

| Table | Title                         | Page |

|-------|-------------------------------|------|

| 16-4  | Bit Manipulation Instructions |      |

| 16-5  | Control Instructions          |      |

| 16-6  | Instruction Set Summary       |      |

| 16-7  | Opcode Map                    |      |

| 19-1  | MC Order Number               | 245  |

# **Section 1. General Description**

## 1.1 Contents

| 1.2                                                                                              | Introduction24                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.3                                                                                              | Features                                                                                                                                                                  |

| 1.4                                                                                              | MCU Structure                                                                                                                                                             |

| 1.5                                                                                              | Programmable Mask Options                                                                                                                                                 |

| 1.6<br>1.6.1<br>1.6.2                                                                            | Operating Modes                                                                                                                                                           |

| 1.7<br>1.7.1<br>1.7.2<br>1.7.3<br>1.7.4<br>1.7.5<br>1.7.5.<br>1.7.5.<br>1.7.5.<br>1.7.6<br>1.7.7 | 2       Ceramic Resonator Oscillator       .31         3       External Clock       .31         RESET       .31         IRQ/V <sub>PP</sub> .31         PA0-PA6       .32 |

| 1.7.9<br>1.7.10<br>1.7.11                                                                        |                                                                                                                                                                           |

| 1.7.12<br>1.7.13<br>1.7.14<br>1.7.15                                                             | 2       TXP and RXP       .33         3       IMAX       .33         4       V <sub>PGC</sub> .34                                                                         |

| 1.7.16                                                                                           |                                                                                                                                                                           |

|                                                                                                  |                                                                                                                                                                           |

MC68HC705V12 — Rev. 3.0

## **General Description**

| 1.7.17 | VGVREF                                                     | 34 |

|--------|------------------------------------------------------------|----|

| 1.7.18 | MAJA(B)1+, MAJA(B)1-, MAJA(B)2+,                           |    |

|        | and MAJA(B)2                                               | 34 |

| 1.7.19 | MINA(B,C,D)1, $MINA(B,C,D)2+$ , and $MINA(B,C,D)2-$ .      | 34 |

| 1.8    | Power Supply Pin Connections                               | 35 |

| 1.9    | Decoupling Recommendations                                 | 35 |

| 1.9.1  | V <sub>DD</sub> to V <sub>SSD</sub> — MCU Internal Digital |    |

|        | Power Decoupling                                           | 36 |

| 1.9.2  | V <sub>CCA</sub> to V <sub>SSA</sub> — Analog Subsystem    |    |

|        | Power Supply Pins                                          | 36 |

### 1.2 Introduction

The Motorola MC68HC705V12 microcontroller is a custom M68HC05-based MCU featuring a byte data link controller (BDLC) module and on-chip power regulation for the on-chip gauge drivers. The device is available packaged in a 68-pin plastic leaded chip carrier (PLCC).

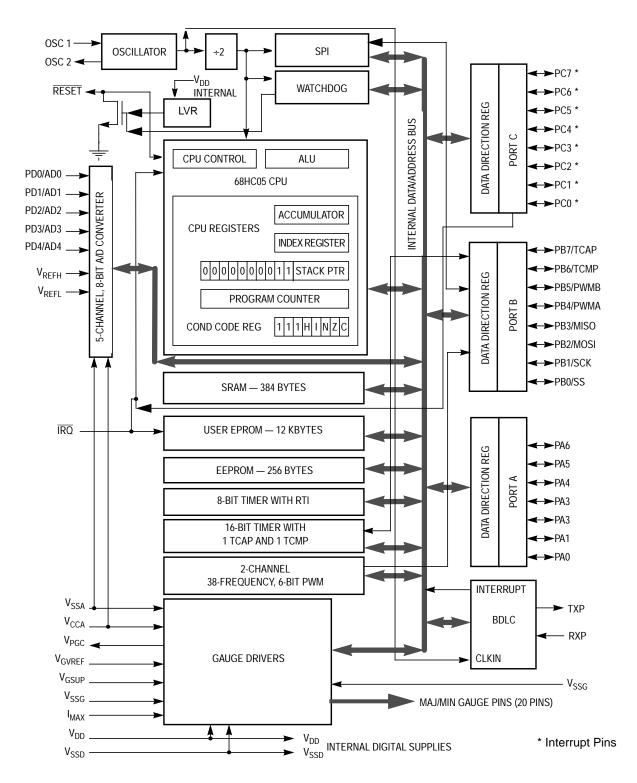

A functional block diagram of the MC68HC705V12 is shown in **Figure 1-1**.

### 1.3 Features

Features of the MC68HC705V12 include:

- M68HC05 core with on-chip oscillator for crystal/ceramic resonator

- 12 Kbytes of user erasable programmable read-only memory (EPROM) and 384 bytes of user random-access memory (RAM)

- 256 bytes of byte, block, or bulk electrically erasable programmable read-only memory (EEPROM)

- Byte data link controller (BDLC) module

- 5-channel, 8-bit analog-to-digital (A/D) converter

- Serial peripheral interface (SPI)

Advance Information MC68HC705V12 — Rev. 3.0

- 8-bit timer with real-time interrupt (RTI)

- 16-bit timer with one input capture and one output compare

- Two 38-frequency, 6-bit pulse width modulators (PWMs)

- Mask option register (MOR) selectable computer operating properly (COP) watchdog system

- 23 general-purpose input/output (I/O) pins:

- Eight I/O pins with interrupt wakeup capability

- Eight I/O pins multiplexed with timer, PWMs, and SPI pins

- Seven general-purpose I/O pins

- Five input-only pins multiplexed with analog to digital (A/D)

- On-chip H-bridge driver circuitry to drive six gauges:

- Four minor gauges

- Two major gauges

- MOR selectable low-voltage reset (LVR)

- Power-saving stop mode and wait mode instructions (MOR selectable STOP instruction disable)

### 1.4 MCU Structure

The overall block diagram of the MC68HC705V12 is shown in Figure 1-1.

#### **NOTE:**

A line over a signal name indicates an active low signal. For example, RESET is active high and RESET is active low. Any reference to voltage, current, or frequency specified in the following sections will refer to the nominal values. The exact values and their tolerance or limits are specified in Section 17. Electrical Specifications.

Figure 1-1. MC68HC705V12 Block Diagram

Advance Information

MC68HC705V12 — Rev. 3.0

## 1.5 Programmable Mask Options

These mask options are programmable via the MOR (see 12.5 EPROM Programming):

- Sensitivity on IRQ interrupt, edge- and level-sensitive or edge-sensitive only

- Selectable COP watchdog system enable/disable

- Selectable low-voltage reset (LVR) to hold the central processor unit (CPU) in reset

- Selectable STOP instruction disable

The mask options are provided through individual bits within the mask option register which is located and programmed as part of the EPROM array.

## 1.6 Operating Modes

The MCU has two modes of operation intended for users:

- User mode

- · Bootloader mode

These modes are briefly described in the following subsections.

#### 1.6.1 User Mode

This mode is the intended mode of operation for executing user firmware. All user mode functions are as described in this document.

#### 1.6.2 Bootloader Mode

This mode is used for programming the on-chip erasable programmable read-only memory (EPROM). See **Section 12. EPROM and EEPROM** for more details on EPROM programming.

## 1.7 Functional Pin Descriptions

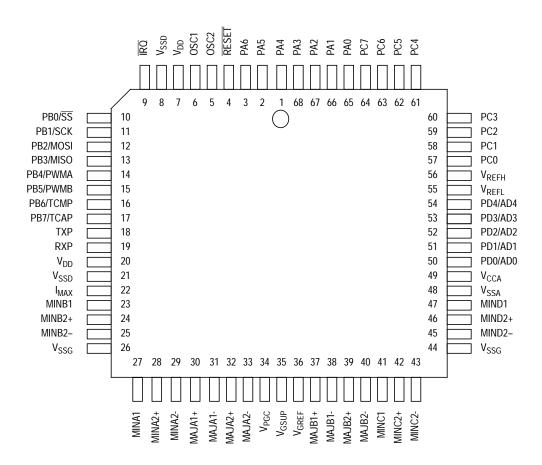

The pinout for the MC68HC705V12 is shown in **Figure 1-2** and is followed by a functional description of each pin.

Figure 1-2. Pin Assignments (68-Pin PLCC Package)

## 1.7.1 $V_{DD}$ and $V_{SSD}$

These pins provide power to all the microcontroller's digital circuits. The short rise and fall times of the MCU supply current transients place very high short-duration current demands on the internal power supply. To prevent noise problems, special care should be taken to provide good power supply bypassing at the MCU by using bypass capacitors with good high-frequency characteristics that are positioned as close to the

Advance Information MC68HC705V12 — Rev. 3.0

MCU supply pins as possible. Two sets of  $V_{DD}$  and  $V_{SS}$  pins are required to maintain on-chip supply noise within acceptable limits. Each supply pin pair will require its own decoupling capacitor. These are high-current pins.

## 1.7.2 V<sub>SSA</sub>

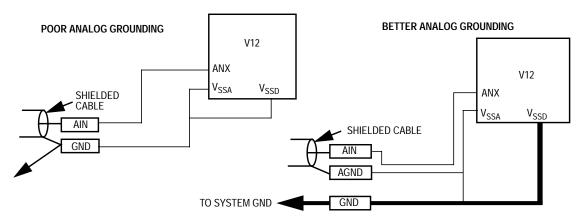

V<sub>SSA</sub> is a separate ground pad which provides a ground return for the analog-to-digital (A/D) subsystem and the digital-to-analog (D/A) gauge subsystem. To prevent digital noise contamination, this pin should be connected directly to a low-impedance ground reference point.

## 1.7.3 V<sub>CCA</sub>

$V_{CCA}$  is a separate supply pin providing power to the analog subsystems of the A/D converter and gauge drivers. This pin must be connected to the  $V_{DD}$  pin externally. To prevent contamination from the digital supply, this pin should be adequately decoupled to a low-impedance ground reference.

### 1.7.4 $V_{REFH}$ and $V_{REFL}$

$V_{REFH}$  is the positive (high) reference voltage for the A/D subsystem.  $V_{REFL}$  is the negative (low) reference voltage for the A/D subsystem.  $V_{REFH}$  and  $V_{REFL}$  should be isolated from the digital supplies to prevent any loss of accuracy from the A/D converter.

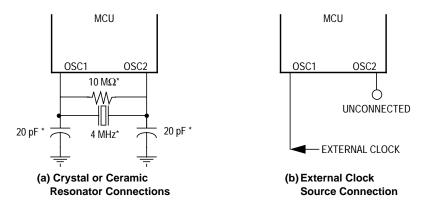

### 1.7.5 OSC1 and OSC2

The OSC1 and OSC2 pins are the connections for the on-chip oscillator. OSC1 is the input to the oscillator inverter. The output (OSC2) will always reflect OSC1 inverted except when the device is in stop mode which forces OSC2 high.

The OSC1 and OCS2 pins can accept these sets of components:

- 1. A crystal as shown in Figure 1-3(a)

- 2. A ceramic resonator as shown in Figure 1-3(a)

- 3. An external clock signal as shown in Figure 1-3(b)

The frequency,  $f_{OSC}$ , of the oscillator or external clock source is divided by two to produce the internal operating frequency,  $f_{OP}$ .

<sup>\*</sup>Values shown are typical. For further information, consult the crystal oscillator vendor.

Figure 1-3. Oscillator Connections

### 1.7.5.1 Crystal Oscillator

The circuit in **Figure 1-3**(a) shows a typical oscillator circuit for an AT-cut, parallel resonant crystal.

### **NOTE:**

The crystal manufacturer's recommendations should be followed, as the crystal parameters determine the external component values required to provide maximum stability and reliable startup.

The load capacitance values used in the oscillator circuit design should include all stray capacitances. The crystal and components should be mounted as close as possible to the pins for startup stabilization and to minimize output distortion and radiated emissions.

### 1.7.5.2 Ceramic Resonator Oscillator

In cost-sensitive applications, a ceramic resonator can be used in place of the crystal. The circuit in **Figure 1-3**(a) can be used for a ceramic resonator.

#### NOTE:

The resonator manufacturer's recommendations should be followed, as the resonator parameters determine the external component values required for maximum stability and reliable starting.

The load capacitance values used in the oscillator circuit design should include all stray capacitances. The ceramic resonator and components should be mounted as close as possible to the pins for startup stabilization and to minimize output distortion and radiated emissions.

#### 1.7.5.3 External Clock

An external clock from another CMOS-compatible device can be connected to the OSC1 input. The OSC2 pin should be left unconnected, as shown in **Figure 1-3**(b).

#### 1.7.6 **RESET**

This pin can be used as an input to reset the MCU to a known startup state by pulling it to the low state. The RESET pin contains an internal Schmitt trigger to improve its noise immunity as an input. The RESET pin has an internal pulldown device that pulls the RESET pin low when there is a COP watchdog reset, power-on reset (POR), illegal address reset, a disabled STOP instruction reset, or an internal low-voltage reset. Refer to Section 5. Resets.

## 1.7.7 **IRQ/V**<sub>PP</sub>

This input pin drives the asynchronous maskable interrupt request (IRQ) function of the CPU. The IRQ interrupt function has a programmable mask option to select either negative edge-sensitive triggering or both negative edge-sensitive and low level-sensitive triggering. The IRQ input requires an external resistor to  $V_{DD}$  for wire-OR operation, if desired. If

MC68HC705V12 — Rev. 3.0

the  $\overline{IRQ}$  pin is not used, it must be tied to the  $V_{DD}$  supply. The  $\overline{IRQ}$  pin contains an internal Schmitt trigger as part of its input to improve noise immunity. Each of the PC0–PC7 I/O pins may be connected as an OR function with the IRQ interrupt function. This capability allows keyboard scan applications where the transitions on the I/O pins will behave the same as the  $\overline{IRQ}$  pin. The edge or level sensitivity selected by a mask option for the  $\overline{IRQ}$  pin does not apply to the port C I/O pin interrupt. The I/O pin interrupt is always negative edge-sensitive. See **Section 4. Interrupts** for more details on the interrupts.

This pin is also used to provide the programming voltage for the EPROM array. See **Section 12. EPROM and EEPROM** for more details on EPROM programming.

### 1.7.8 PA0-PA6

These seven I/O lines comprise port A. The state of any pin is software programmable, and all port A lines are configured as inputs during power-on or reset. See **Section 7. Parallel Input/Output (I/O)** for more details on the I/O ports.

### 1.7.9 PB0-PB3 (SPI Pins), PB4/PWMA, PB5/PWMB, PB6/TCMP, and PB7/TCAP

These eight I/O lines comprise port B. The state of any pin is software programmable, and all port B lines are configured as inputs during power-on or reset. See **Section 7. Parallel Input/Output (I/O)** for more details on the I/O ports.

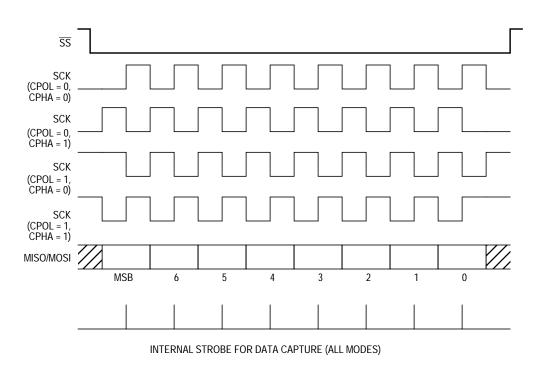

PB0–PB3 are shared SPI functions. See **Section 10. Serial Peripheral Interface (SPI)** for more details concerning the operation of the SPI and configuration of these pins.

PB6 and PB7 are also shared with timer functions. The TCAP pin controls the input capture feature for the on-chip 16-bit timer. The TCMP pin provides an output for the output compare feature of the on-chip 16-bit timer. See **Section 9. 16-Bit Timer** for more details on the operation of the timer subsystem.

PB4 and PB5 are shared with the PWM output pins (PWMA and PWMB). See **Section 11. Pulse Width Modulators (PWMs)** for more details on the operation of the PWMs.

#### 1.7.10 PC0-PC7

These eight I/O lines comprise port C. The state of any pin is software programmable and all port C lines are configured as inputs during power-on or reset. All eight pins are connected via an internal gate to the IRQ interrupt function. When the IRQ interrupt function is enabled, all the port C pins will act as negative edge-sensitive IRQ sources. See Section 7. Parallel Input/Output (I/O) for more details on the I/O ports.

#### 1.7.11 PD0-PD4/AD0-AD4

When the A/D converter is disabled, PD0–PD4 are general-purpose input pins. The A/D converter is disabled upon exiting from reset. When the A/D converter is enabled, one of these pins is the analog input to the A/D converter. The A/D control register contains control bits to direct which of the analog inputs are to be converted at any one time. A digital read of this pin when the A/D converter is enabled results in a read of logical 0 from the selected analog pin. A digital read of the remaining pins gives their correct (digital) values. See Section 13.

Analog-to-Digital (A/D) Converter for more details on the operation of the A/D subsystem.

#### 1.7.12 TXP and RXP

These pins provide the I/O interface for the byte data link controller (BDLC) subsystem. See **Section 14. Byte Data Link Controller – Digital (BDLC–D)** for more details on the operation of the BDLC.

## 1.7.13 I<sub>MAX</sub>

This pin is used to define the maximum coil current in the gauges by connecting a resistor from this pin  $(R_{MAX})$  to ground as shown in 15.7 Coil Sequencer and Control.

MC68HC705V12 — Rev. 3.0

## **General Description**

## 1.7.14 V<sub>PGC</sub>

This pin is the gauge power control pin for the external pass device. Refer to 15.7 Coil Sequencer and Control.

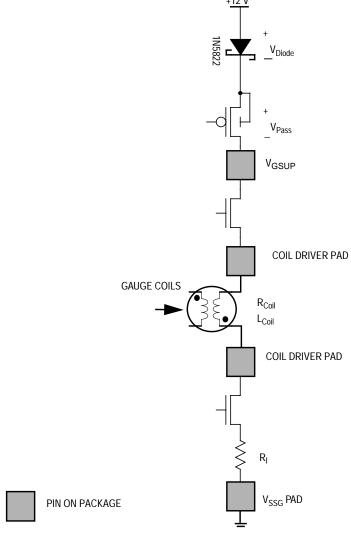

### 1.7.15 V<sub>GSUP</sub>

This pin is the regulated gauge voltage input. Refer to **15.7 Coil Sequencer and Control**.

## 1.7.16 V<sub>SSG</sub>

Two pins are provided for a separate gauge driver ground, V<sub>SSG</sub>. Used as the current return only for the coil driver circuitry, it is a high-current pin.

## 1.7.17 V<sub>GVREF</sub>

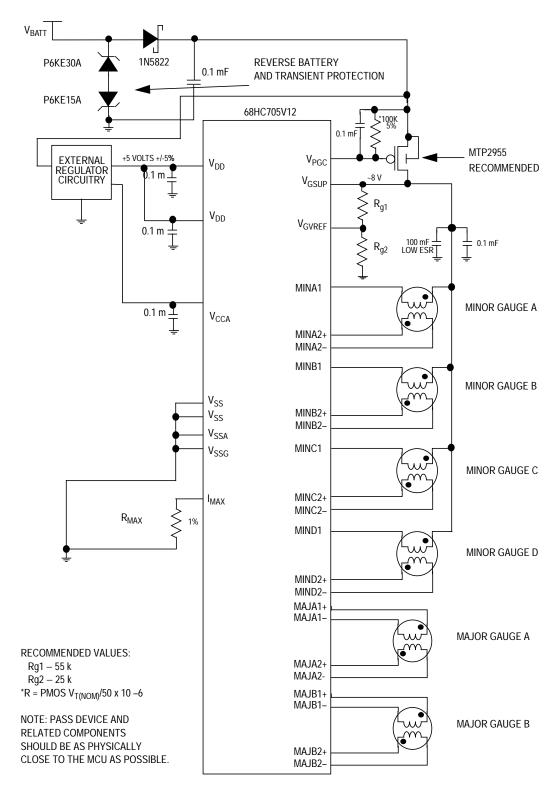

This pin is the feedback pin for the gauge power regulator. External resistors as shown in **Figure 15-14. Sample Gauge Connections to the MC68HC705V12** are used to set the gauge input voltage at pin  $V_{\text{GSUP}}$ .

### 1.7.18 MAJA(B)1+, MAJA(B)1-, MAJA(B)2+, and MAJA(B)2-

These pins are the full H-bridge coil driver pins. The A or B refer to pins associated with major gauge A or gauge B, and pin 1+/– or pin 2+/– refer to coil 1 or coil 2 of that major gauge and the direction of current flow. Refer to 15.3 Gauge System Overview for more details on the operation of these pins.

## 1.7.19 MINA(B,C,D)1, MINA(B,C,D)2+, and MINA(B,C,D)2-

MINA(B,C,D)2+ and MINA(B,C,D)2- are the full H-bridge driver pins used with or for the minor gauges. These pins allow the coil current to be reversed for movement of gauge pointer from 0 to 180 degrees.

Advance Information MC68HC705V12 — Rev. 3.0

MINA(B,C,D)1 is the low-side driver pin used with the minor gauges. The current flow through the coil is restricted to one direction. Refer to **15.3 Gauge System Overview** for more details on the operation of these pins.

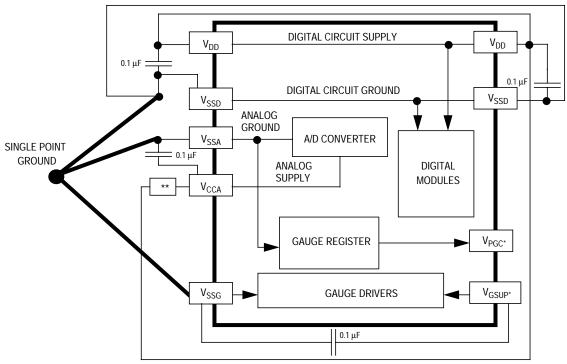

## 1.8 Power Supply Pin Connections

Refer to Figure 1-4 for a supply decoupling diagram.

<sup>\*</sup> Refer to Section 15. Gauge Drivers for decoupling recommendations.

Figure 1-4. Supply Decoupling Diagram

## 1.9 Decoupling Recommendations

To provide effective decoupling and to reduce radiated RF (radio frequency) emissions, small decoupling capacitors must be located as close to the supply pins as possible. The self-inductance of these capacitors and the parasitic inductance and capacitance of the interconnecting traces determine the self-resonant frequency of the

MC68HC705V12 — Rev. 3.0

<sup>\*\*</sup>Optional supply isolation circuit

decoupling network. A frequency that is too low will reduce decoupling effectiveness and could increase radiated RF emissions from the system. A low value capacitor (470 pF to 0.01  $\mu$ F) placed in parallel with the other capacitors will improve the bandwidth and effectiveness of the network.

### 1.9.1 V<sub>DD</sub> to V<sub>SSD</sub> — MCU Internal Digital Power Decoupling

Decouple with a 0.1  $\mu$ F ceramic or polystyrene cap. If the self-resonance frequency of the decoupling circuit (assume 4 nH per bond wire) is too low, add a 0.01  $\mu$ F or smaller cap in parallel to increase the bandwidth of the decoupling network. Place the smaller cap closest to the V<sub>DD</sub> and V<sub>SSD</sub> pins.

### 1.9.2 V<sub>CCA</sub> to V<sub>SSA</sub> — Analog Subsystem Power Supply Pins

These pins are internally isolated from the digital  $V_{DD}$  and  $V_{SS}$  supplies. The  $V_{SSA}$  pin provides a ground return for the A/D subsystem and portions of the gauge subsystem. The analog supply pins should be appropriately filtered to prevent any external noise affecting the analog subsystems. The  $V_{SSA}$  pin should be brought together with the digital ground at a single point which has a low (HF) impedance to ground to prevent common mode noise problems. If this is not practical, then the  $V_{SSA}$  PCB traces should be routed in such a manner that digital ground return current is impeded from passing through the analog input ground reference as shown in **Figure 1-5**.

Figure 1-5. Single-Sided PCB Example

Advance Information MC68HC705V12 — Rev. 3.0

# **Section 2. Memory Map**

#### 2.1 Contents

| 2.2 | Introduction              |

|-----|---------------------------|

| 2.3 | I/O and Control Registers |

| 2.4 | RAM                       |

| 2.5 | Boot ROM47                |

| 2.6 | EPROM                     |

| 2.7 | EEPROM                    |

| 2.8 | Miscellaneous Register    |

### 2.2 Introduction

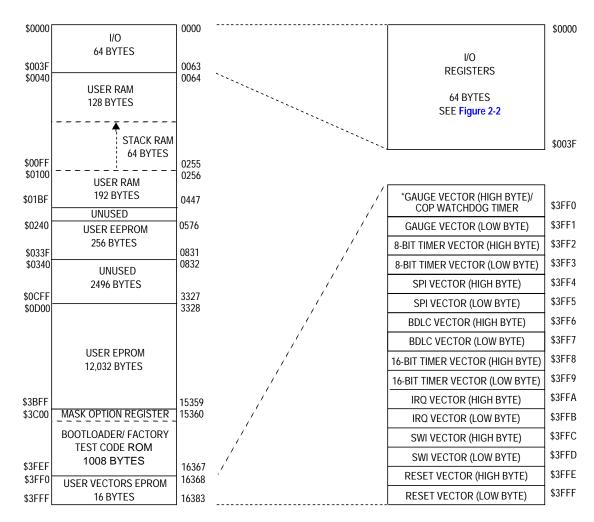

When the MC68HC705V12 is in the single-chip mode, the input/output (I/O) and peripherals, user random-access memory (RAM), electrically erasable programmable read-only memory (EEPROM), and user erasable programmable read-only memory (EPROM) are all active as shown in **Figure 2-1**.

MC68HC705V12 — Rev. 3.0

Advance Information

<sup>\*</sup>Reading \$3FF0 returns the gauge vector EPROM byte. Writing a 0 to \$3FF0, bit 0, resets the COP.

Figure 2-1. MC68HC705V12 Single-Chip Mode Memory Map

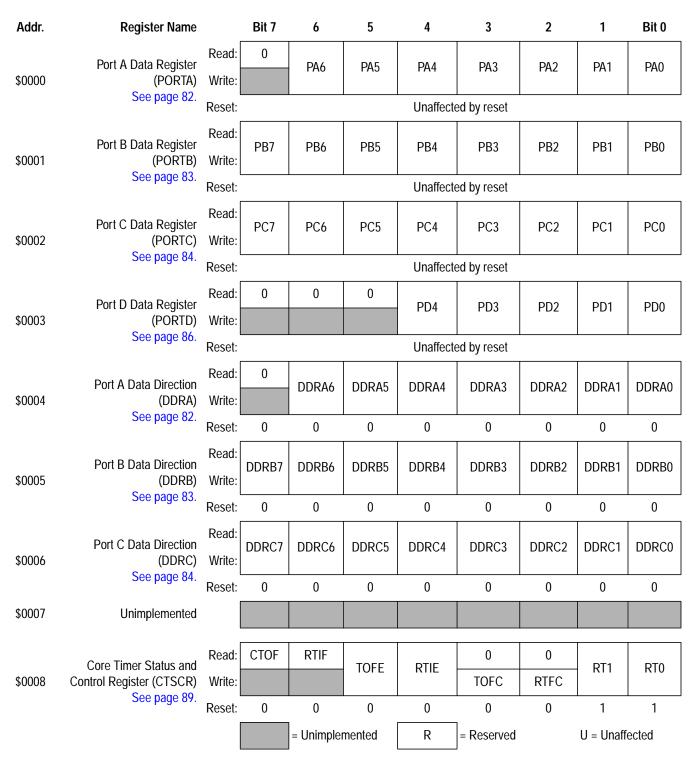

# 2.3 I/O and Control Registers

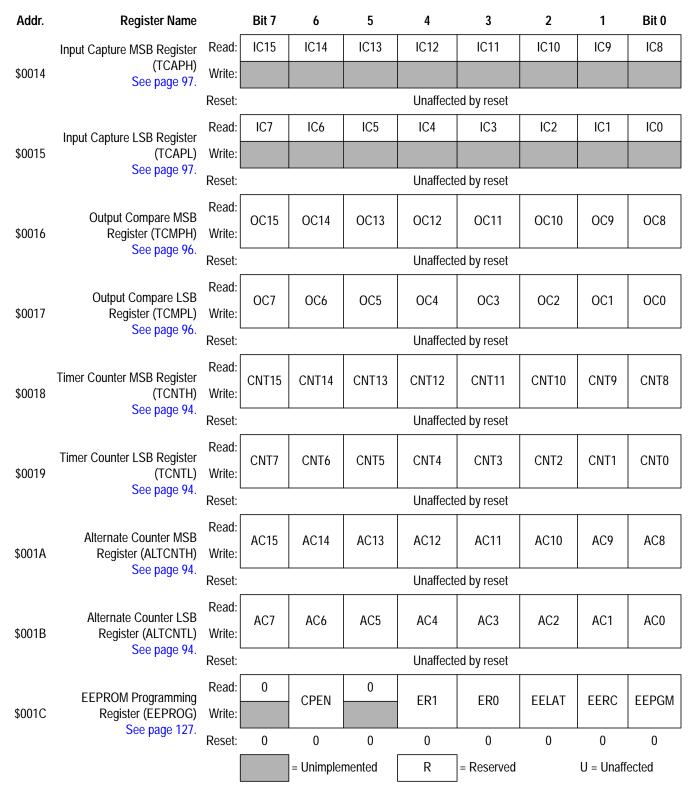

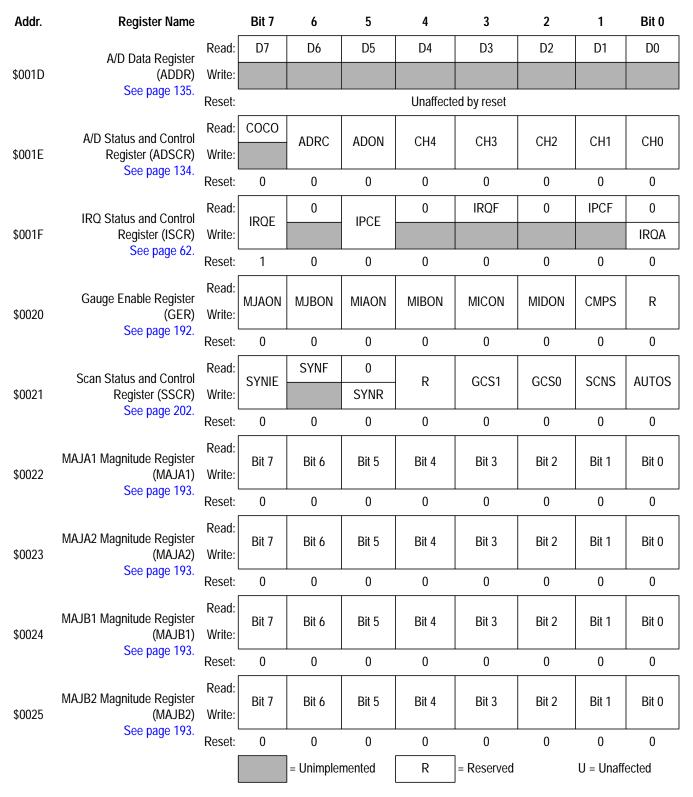

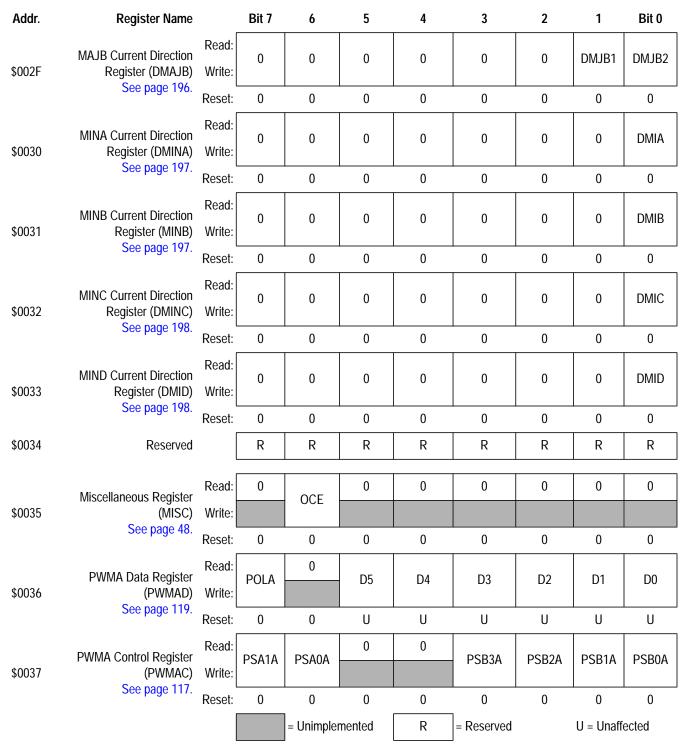

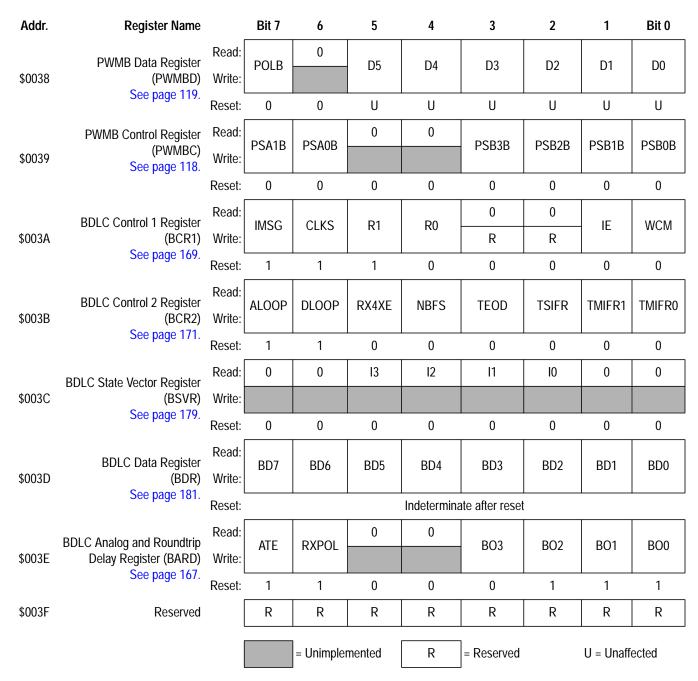

The I/O and control registers reside in locations \$0000–\$003F. The overall organization of these registers is shown in **Figure 2-2**. The bit assignments for each register are shown in **Figure 2-3**. Reading from unimplemented bits will return unknown states, and writing to unimplemented bits will be ignored.

| Port A Data Register               | \$0000 |

|------------------------------------|--------|

| Port B Data Register               | \$0001 |

| Port C Data Register               | \$0002 |

| Port D Data Register               | \$0003 |

| Port A Data Direction Register     | \$0004 |

| Port B Data Direction Register     | \$0005 |

| Port C Data Direction Register     | \$0006 |

| Unused                             | \$0007 |

| 8-Bit Timer Status and Control     | \$0008 |

| 8-Bit Timer Counter Register       | \$0009 |

| SPI Control Register               | \$000A |

| SPI Status Register                | \$000B |

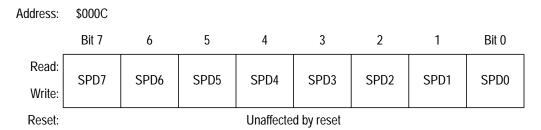

| SPI Data Register                  | \$000C |

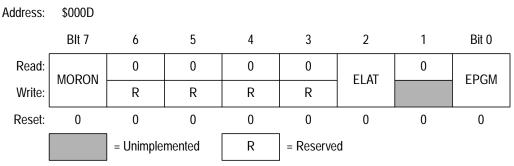

| EPROM Program Register             | \$000D |

| Unimplemented                      | \$000E |

| Unimplemented                      | \$000F |

| Unimplemented                      | \$0010 |

| Unimplemented                      | \$0011 |

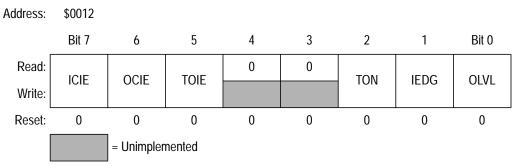

| 16-Bit Timer Control Register      | \$0012 |

| 16-Bit Timer Status Register       | \$0013 |

| Input Capture Register (High)      | \$0014 |

| Input Capture Register (Low)       | \$0015 |

| Output Compare Register (High)     | \$0016 |

| Output Compare Register (Low)      | \$0017 |

| 16-Bit Timer Count Register (High) | \$0018 |

| 16-Bit Timer Count Register (Low)  | \$0019 |

| Alternate Count Register (High)    | \$001A |

| Alternate Count Register (Low)     | \$001B |

| EEPROM Program Register            | \$001C |

| A/D Data Register                  | \$001D |

| A/D Status and Control Register    | \$001E |

| IRQ Status and Control Register    | \$001F |

| Gauge Enable Register — GER          | \$0020 |

|--------------------------------------|--------|

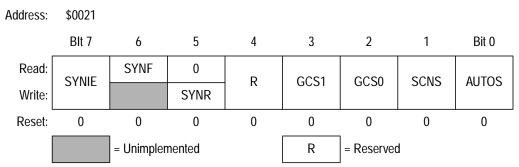

| Scan Status & Control Reg — SSCR     | \$0021 |

| Magnitude Register — MAJA1           | \$0022 |

| Magnitude Register — MAJA2           | \$0023 |

| Magnitude Register — MAJB1           | \$0024 |

| Magnitude Register — MAJB2           | \$0025 |

| Magnitude Register — MINA1           | \$0026 |

| Magnitude Register — MINA2           | \$0027 |

| Magnitude Register — MINB1           | \$0028 |

| Magnitude Register — MINB2           | \$0029 |

| Magnitude Register — MINC1           | \$002A |

| Magnitude Register — MINC2           | \$002B |

| Magnitude Register — MIND1           | \$002C |

| Magnitude Register — MIND2           | \$002D |

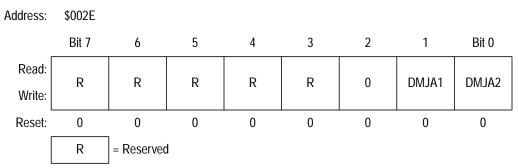

| Current Direction Register — DMAJA   | \$002E |

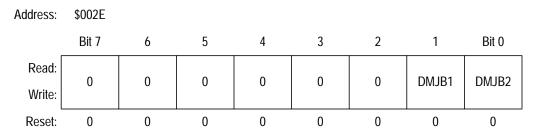

| Current Direction Register — DMAJB   | \$002F |

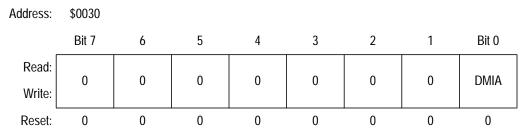

| Current Direction Register — DMINA   | \$0030 |

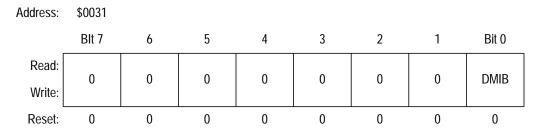

| Current Direction Register — DMINB   | \$0031 |

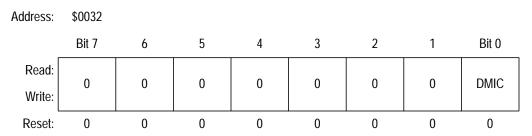

| Current Direction Register — DMINC   | \$0032 |

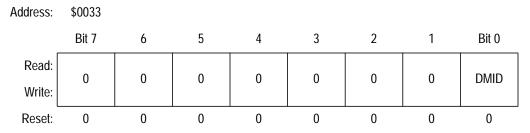

| Current Direction Register — DMIND   | \$0033 |

| Reserved                             | \$0034 |

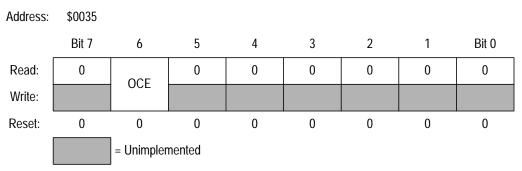

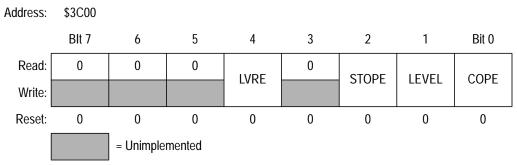

| Miscellaneous Register               | \$0035 |

| PWMA Data Register                   | \$0036 |

| PWMA Control Register                | \$0037 |

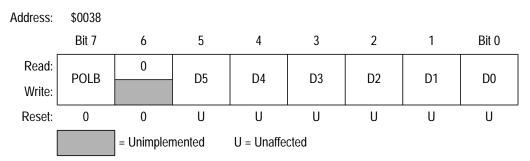

| PWMB Data Register                   | \$0038 |

| PWMB Control Register                | \$0039 |

| BDLC Control Register 1              | \$003A |

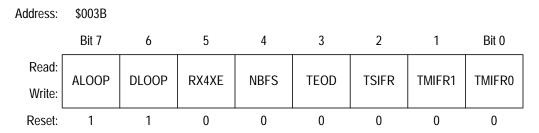

| BDLC Control Register 2              | \$003B |

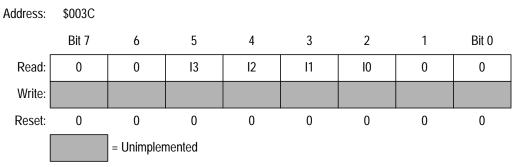

| BDLC State Vector Register           | \$003C |

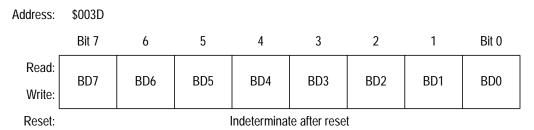

| BDLC Data Register                   | \$003D |

| BDLC Analog Roundtrip Delay Register | \$003E |

| Reserved                             | \$003F |

|                                      | J      |

Figure 2-2. MC68HC705V12 I/O Registers Memory Map

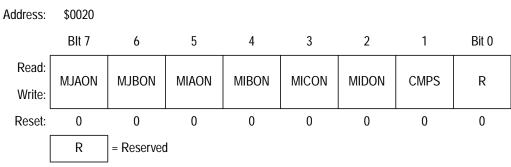

Figure 2-3. I/O and Control Registers (Sheet 1 of 7)

Advance Information

MC68HC705V12 — Rev. 3.0

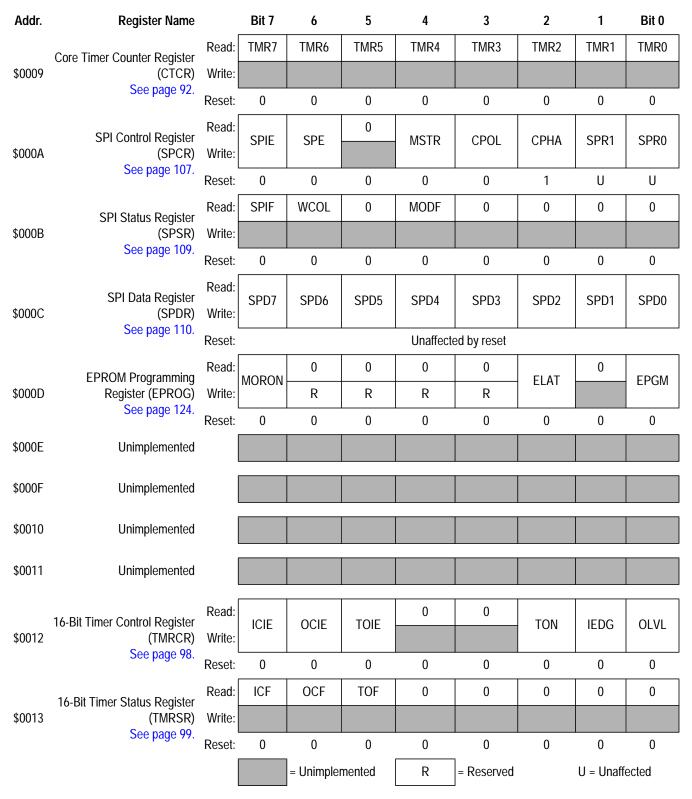

Figure 2-3. I/O and Control Registers (Sheet 2 of 7)

MC68HC705V12 — Rev. 3.0

**Advance Information**

Figure 2-3. I/O and Control Registers (Sheet 3 of 7)

Advance Information MC68HC705V12 — Rev. 3.0

Figure 2-3. I/O and Control Registers (Sheet 4 of 7)

MC68HC705V12 — Rev. 3.0

Advance Information

| Addr.  | Register Name                                        |                 | Bit 7 | 6         | 5      | 4     | 3          | 2     | 1         | Bit 0 |

|--------|------------------------------------------------------|-----------------|-------|-----------|--------|-------|------------|-------|-----------|-------|

| \$0026 | MINA1 Magnitude Register<br>(MINA1)                  | Read:<br>Write: | Bit 7 | Bit 6     | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1     | Bit 0 |

|        | See page 193.                                        |                 | 0     | 0         | 0      | 0     | 0          | 0     | 0         | 0     |

| \$0027 |                                                      | Read:<br>Write: | Bit 7 | Bit 6     | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1     | Bit 0 |

|        | See page 193.                                        | Reset:          | 0     | 0         | 0      | 0     | 0          | 0     | 0         | 0     |

| \$0028 | MINB1 Magnitude Register<br>(MINB1)<br>See page 193. | Read:<br>Write: | Bit 7 | Bit 6     | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1     | Bit 0 |

|        | 3ee page 173.                                        | Reset:          | 0     | 0         | 0      | 0     | 0          | 0     | 0         | 0     |

| \$0029 | MINB2 Magnitude Register<br>(MINB2)                  | Read:<br>Write: | Bit 7 | Bit 6     | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1     | Bit 0 |

|        | See page 193.                                        | Reset:          | 0     | 0         | 0      | 0     | 0          | 0     | 0         | 0     |

| \$002A | MINC1 Magnitude Register<br>(MINC1)                  | Read:<br>Write: | Bit 7 | Bit 6     | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1     | Bit 0 |

|        | See page 193.                                        | Reset:          | 0     | 0         | 0      | 0     | 0          | 0     | 0         | 0     |

| \$002B | MINC2 Magnitude Register<br>(MINC2)<br>See page 193. | Read:<br>Write: | Bit 7 | Bit 6     | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1     | Bit 0 |

|        | See page 173.                                        | Reset:          | 0     | 0         | 0      | 0     | 0          | 0     | 0         | 0     |

| \$002C | MIND1 Magnitude Register<br>(MIND1)                  | Read:<br>Write: | Bit 7 | Bit 6     | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1     | Bit 0 |

|        | See page 193.                                        | Reset:          | 0     | 0         | 0      | 0     | 0          | 0     | 0         | 0     |